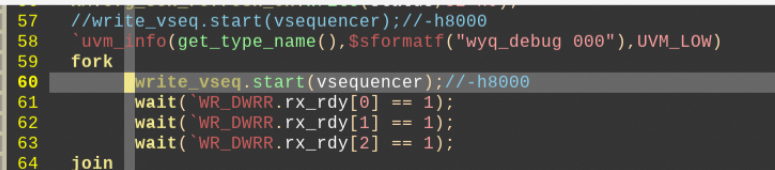

现象:

代码选择打开57行,注释掉60行执行,结果58行不会打印。

代码选择打开60行,注释57行执行,结果58行正常打印。

sequence的执行需要时间!!!

SV中代码57行切换到60行的区别?

这两行代码的位置变化带来了完全不同的执行行为:

🔄 执行顺序的根本区别

第57行(注释掉的位置)

57 //write_vseq.start(vsequencer);//-h8000 [顺序执行]

58 `uvm_info(get_type_name(),$sformatf("wya_debug 000"),UVM_LOW)

59 fork

60 write_vseq.start(vsequencer);//-h8000 [并行执行]

61 wait(WR_DWRR.rx_rdy[0] == 1);

62 wait(WR_DWRR.rx_rdy[1] == 1);

63 wait(WR_DWRR.rx_rdy[2] == 1);

64 join

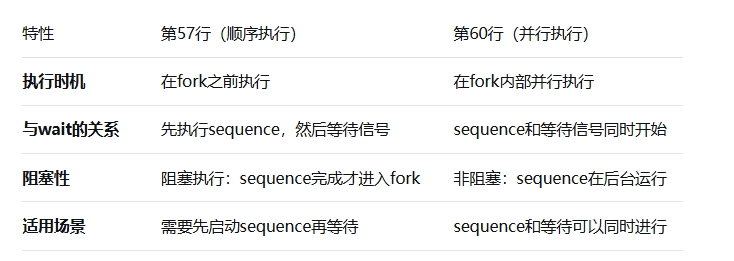

📊 两种位置的对比

🎯 具体行为分析

情况1:第57行(顺序执行)

//write_vseq.start(vsequencer); // 1. 先执行sequence(如果取消注释)

`uvm_info("DEBUG", "wya_debug 000", UVM_LOW); // 2. 打印信息

fork // 3. 然后开始并行等待wait(WR_DWRR.rx_rdy[0] == 1);wait(WR_DWRR.rx_rdy[1] == 1); wait(WR_DWRR.rx_rdy[2] == 1);

join

// 4. 等待所有信号就绪

执行流程:sequence → 打印 → 等待信号

情况2:第60行(并行执行)

`uvm_info("DEBUG", "wya_debug 000", UVM_LOW); // 1. 先打印信息

fork // 2. 并行执行以下操作write_vseq.start(vsequencer); // 2.1 启动sequencewait(WR_DWRR.rx_rdy[0] == 1); // 2.2 同时等待信号wait(WR_DWRR.rx_rdy[1] == 1);wait(WR_DWRR.rx_rdy[2] == 1);

join // 3. 等待sequence完成且所有信号就绪

执行流程:打印 → (sequence + 等待信号) 并行执行

⏱️ 时序差异

第57行位置的时序(如果取消注释)

时间轴:

0ns: 启动write_vseq sequence→ sequence执行各种操作→ 可能驱动信号、产生流量

???ns: sequence完成执行→ 打印"wya_debug 000"→ 开始等待rx_rdy信号

第60行位置的时序

时间轴:

0ns: 打印"wya_debug 000"→ 同时:启动write_vseq sequence(后台运行)开始等待rx_rdy[0]信号开始等待rx_rdy[1]信号 开始等待rx_rdy[2]信号→ 等待所有条件满足:sequence完成 + 所有信号就绪

💡 建议的使用方式

使用第57行位置(顺序执行)当:

需要先完成sequence的初始化

sequence执行时间很短

等待信号需要在sequence之后

使用第60行位置(并行执行)当:

sequence可以后台运行

希望尽快开始等待信号

sequence执行时间和信号等待可以重叠

🔧 更好的写法

`uvm_info(get_type_name(), $sformatf("wya_debug 000"), UVM_LOW)forkbeginwrite_vseq.start(vsequencer); // 运行sequence`uvm_info("DEBUG", "Sequence completed", UVM_LOW)endbeginwait(WR_DWRR.rx_rdy[0] == 1);wait(WR_DWRR.rx_rdy[1] == 1);wait(WR_DWRR.rx_rdy[2] == 1);`uvm_info("DEBUG", "All signals ready", UVM_LOW)end

join

// 等待sequence完成并且所有信号就绪

**结论:**从57行移到60行改变了sequence的执行时机,从顺序执行变为并行执行,这会影响程序的同步逻辑和时序行为。

)

)

--从基本介绍,内部原理、应用场景、使用方法,常见问题和解决方案进行深度解析)