SGMII链路中的AC耦合电容摆放位置

目前是有个板子,其上分别有fpga,fpga的gtx口出sgmii千兆以太网链路,通过高速连接器互联,

通常高速差分链路的AC耦合电容放在靠近接收端位置,如果在同一个板内的话没啥疑惑的直接靠近接收端fpga管脚摆放了。但是对于通过连接器互联的模式,是靠近fpga管脚还是摆放在连接器边上呢?fpga的gtx到连接器走线大概4000mil。

询问后,网上有网友给出建议:

1)这种东西莫衷一是,比如pcie,sata什么的协议有规定靠近发射侧方还是接收侧方,主要是为了限制主板厂家方还是板卡厂家方。对于在板的应用,其实没那么玄乎,放在哪里仿真和实测结果都差不多,没有到会决定你板子成败的地步。板卡上,比如pcie板卡,绝大部分厂家靠近金手指连接器放。

2)“通常高速差分链路的AC耦合电容放在靠近接收端“,好像没有这个说法吧。放在发送端的居多。不放心的话,就serdes好了。

3)看过的design guide一般是推荐放在发送端靠近连接器的位置

4)看过一个文章,说是仿真结果来看放在发送端和接收端区别不大,都比放在中间强

5)1.25G的SGMII,速度不高,没那么多讲究,随便摆

6)上面的网友,3.25g的xaui呢?

7)问题也不大,取决于器件的IO性能,我在四层板上内存也稳定跑3.2G

结论:

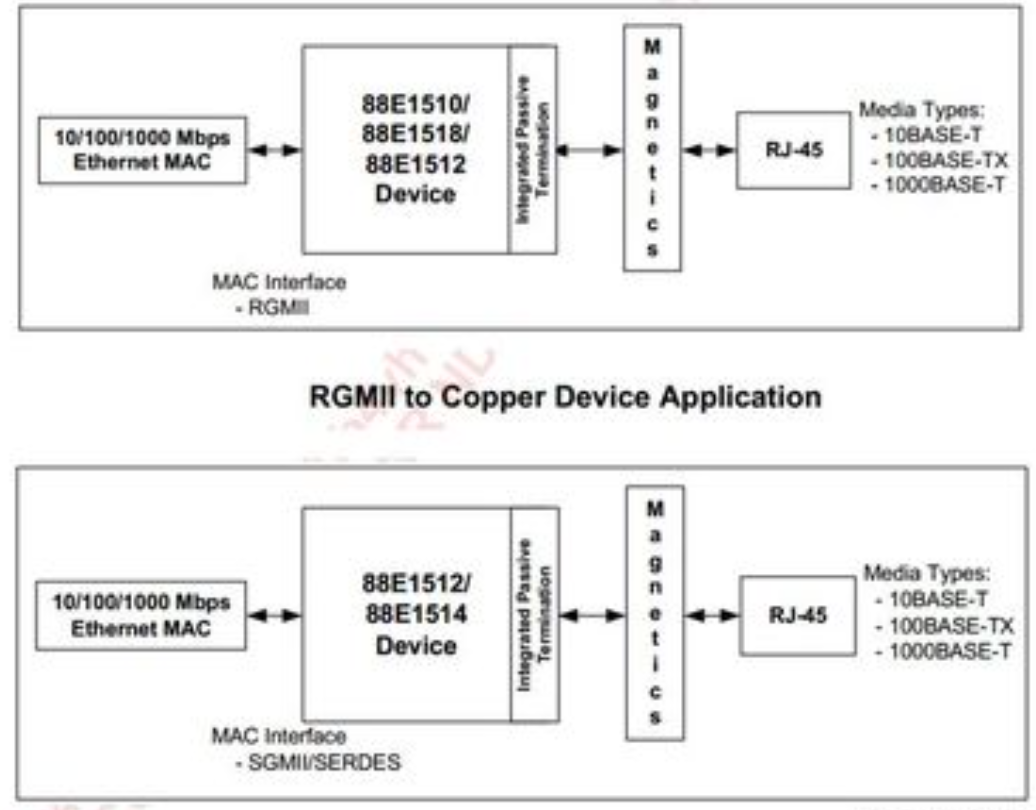

1、SGMII千兆以太网通信,有三组差分线,TX_PN,RX_PN,CLOCK_PN,TX发送时,电容放在FPGA侧;RX接收时,电容放在PHY芯片侧

2、如果有连接器,主板与子板的扣接方式,靠近连接器放置

)

)

转为markdown的方法,把.adoc文件转换为markdown格式)

)

![[智能客服project] AI提示词配置 | 主协调器 | 闲鱼协议工具](http://pic.xiahunao.cn/[智能客服project] AI提示词配置 | 主协调器 | 闲鱼协议工具)

![2025年渗透测试面试题总结-字节跳动[实习]安全研发员(题目+回答)](http://pic.xiahunao.cn/2025年渗透测试面试题总结-字节跳动[实习]安全研发员(题目+回答))

带论文文档1万字以上,文末可获取,系统界面在最后面。)