本原创文章由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处(www.meyesemi.com)

1. 实验简介

实验目的:

完成 PCIE 通信测试。

实验环境:

Window11

PDS2022.2-SP6.4

硬件环境:

MES2L676-100HP

2.实验原理

PG2L100H 集成内置了线速率高达 6.6Gbps 高速串行接口模块,即 HSSTLP。PG2L100H 开发板 提供一个 PCIe x4 接口,PCIE 卡的外形尺寸符合标准 PCIe 卡电气规范要求,可直接在普通 PC 的 x4 PCIe 插槽上使用。

2.1. PCIE 简介

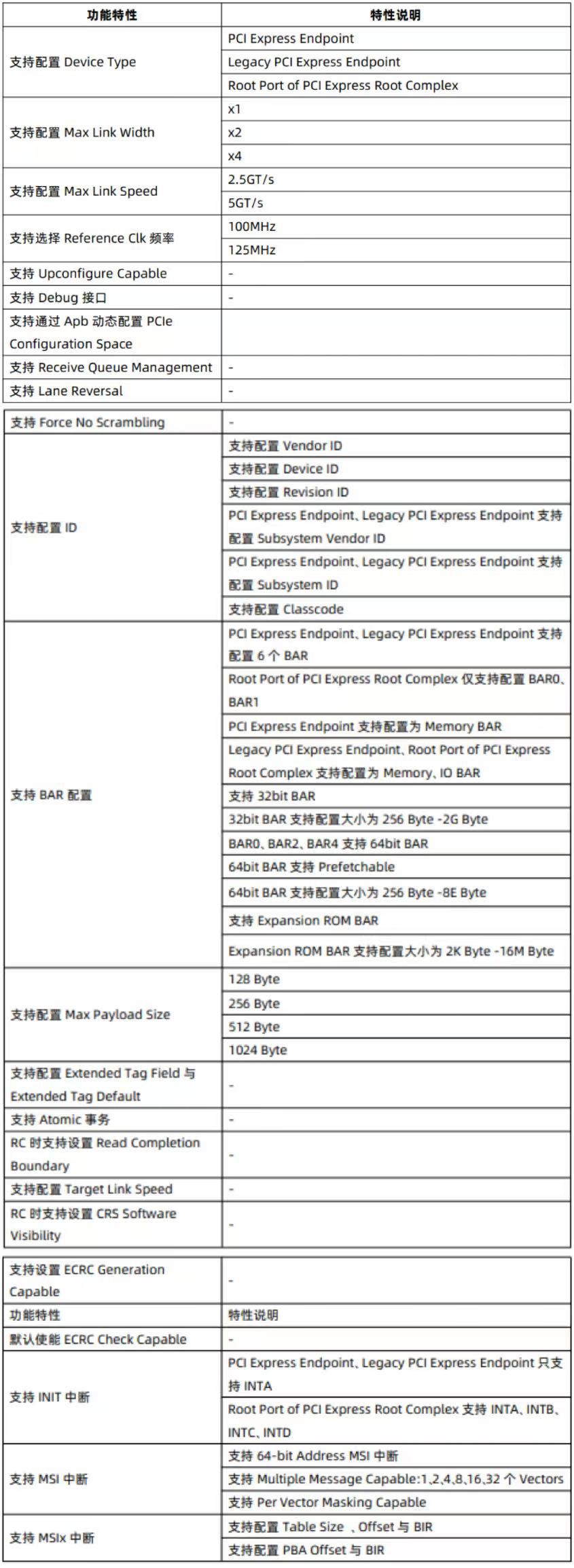

PCIE IP 符合 PCI Express® Base Specification Revision 2.1[8]协议和 PHY Interface for the PCI ExpressTM Architecture Version 2.00[12](数据通路扩展为 32 bits)协议。

3. 工程说明

3.1. 安装 PCIE IP 核

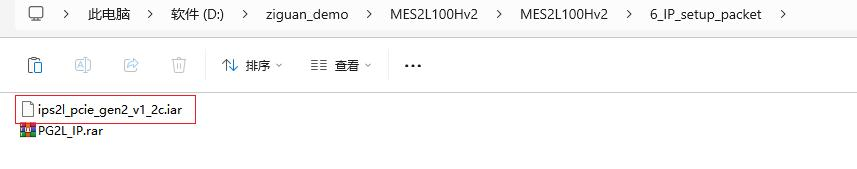

PDS 安装后,需手动添加 PCIE IP,请按以下步骤完成:

PCIE IP 文件:6_IP_setup_packet\ips2l_pcie_gen2_v1_2c.iar

3.2. PCIE 参考设计例程

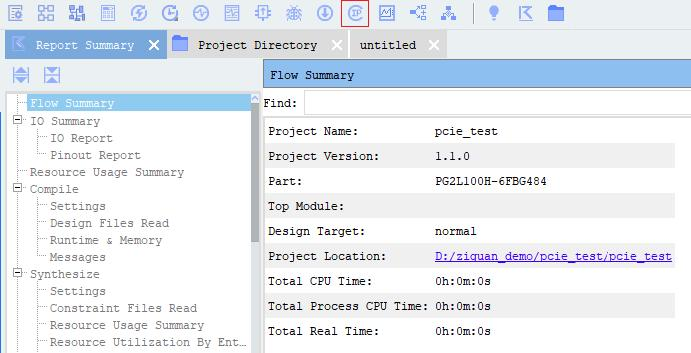

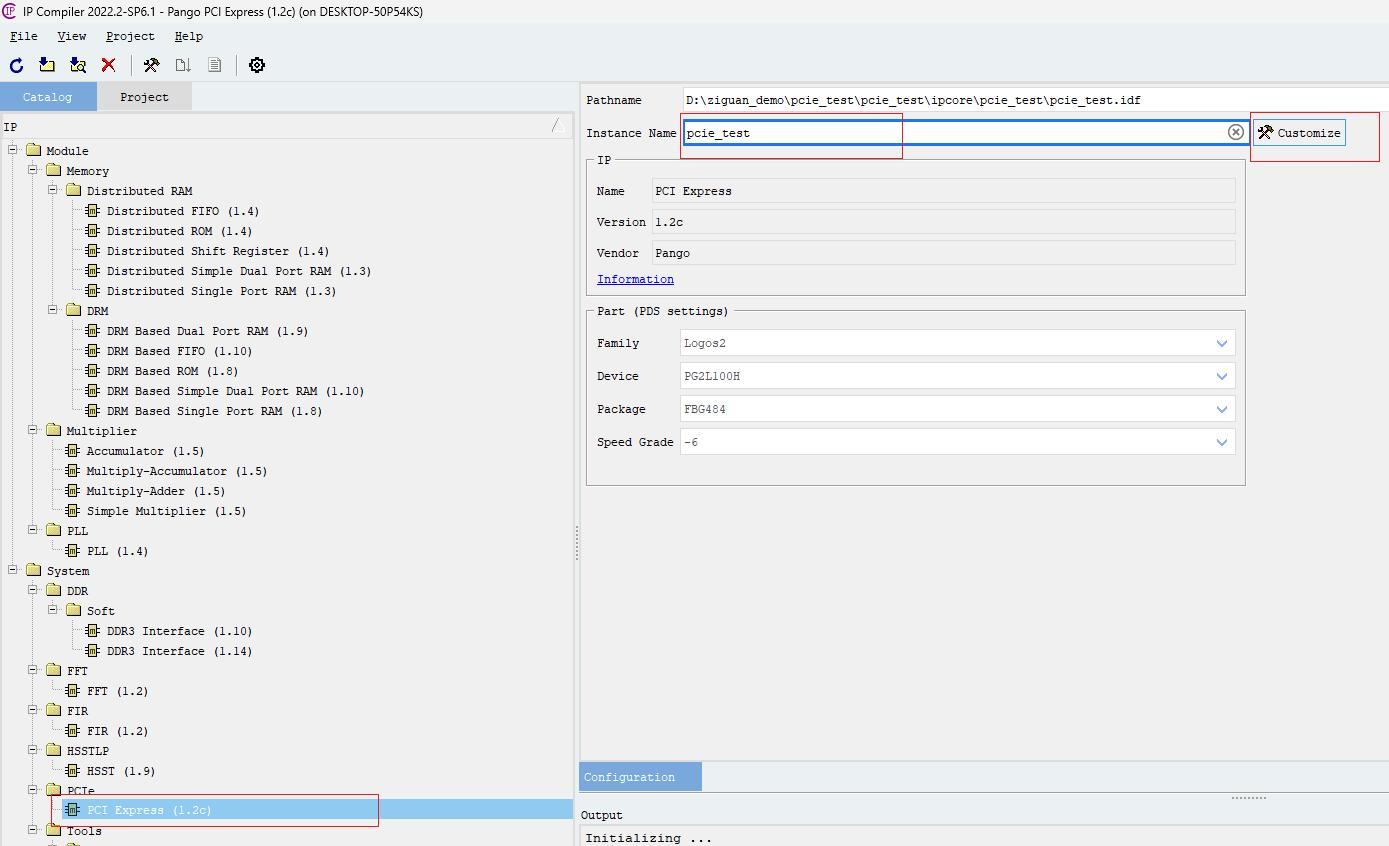

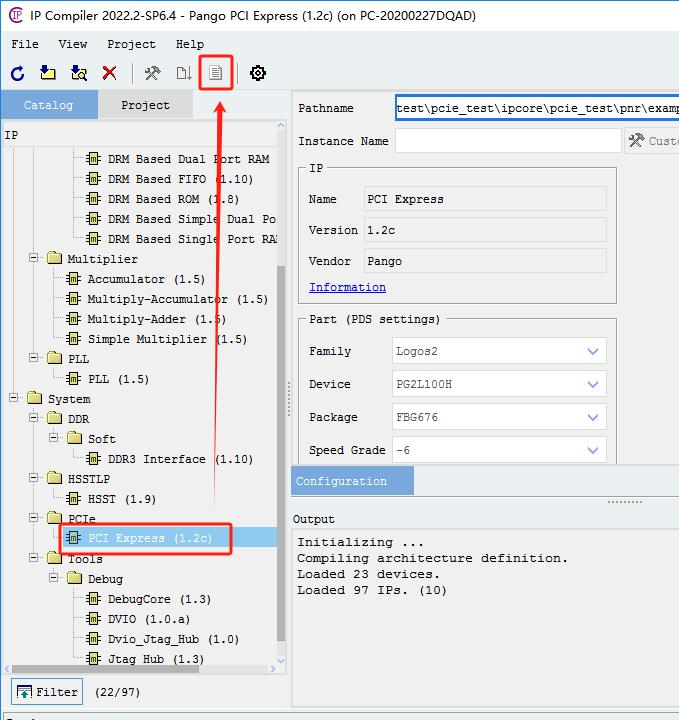

打开 PDS 软件,新建工程 pcie_test,点开如下图标,打开 IP Compiler;

选择 PCIE IP,取名,然后点击 Customize;

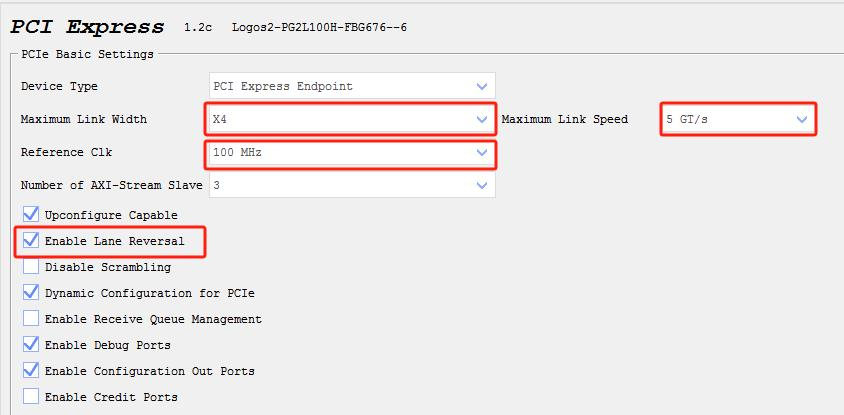

在 PCIE 设置界面中:根据开发板配置 lane 数,可选择 X4,配置参考时钟,可参考下图:

需要注意的是,需要勾选上 Enable Lane Reversal,否则会导致 PCIE 实验失败。

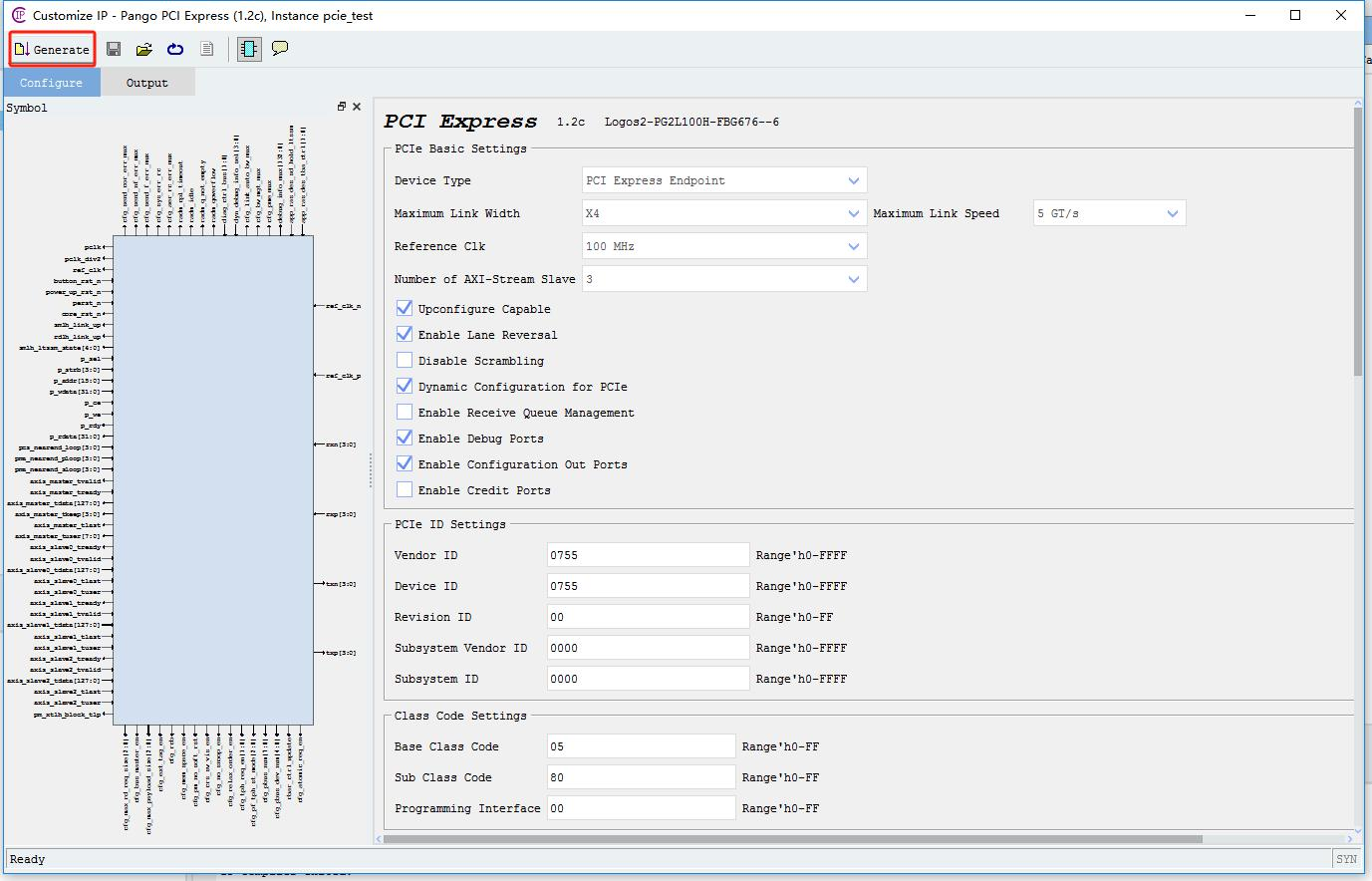

其他设置可保持默认,点击 Generate 生成 PCIE IP。

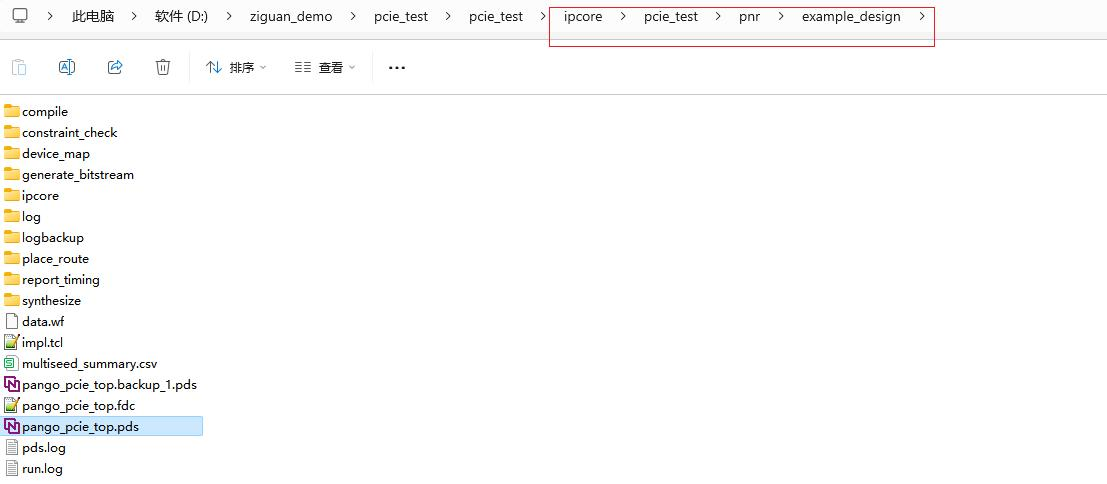

关闭本工程,按此路径打开 Example 工程: Xxxxx\pcie_test\ipcore\pcie_test\pnr\example_design

注意:xxxx 是自己电脑的路径,后面的 pcie_test 及其后面的路径是固定的。

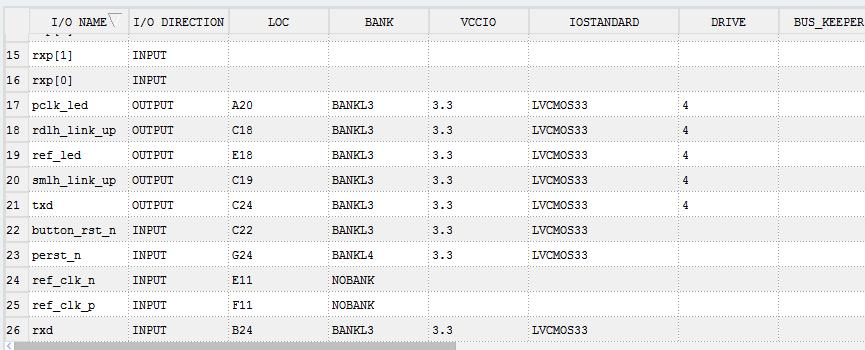

按照开发板管脚,修改相关管脚约束:

注意,像 txp[0],txp[1],rxp[0],rxp[1]等差分信号都不需要约束。其中 txd 和 rxd 是串口。

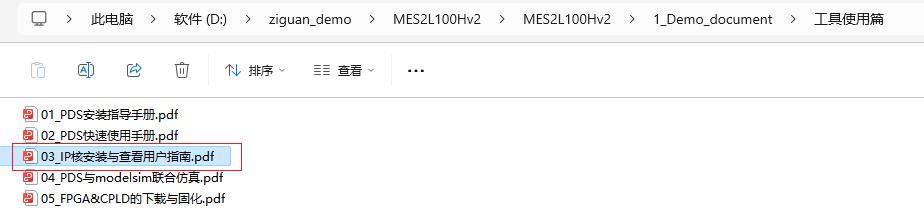

可按以下方式查看 IP 核的用户指南,了解 Example 模块组成;

4. 实验现象

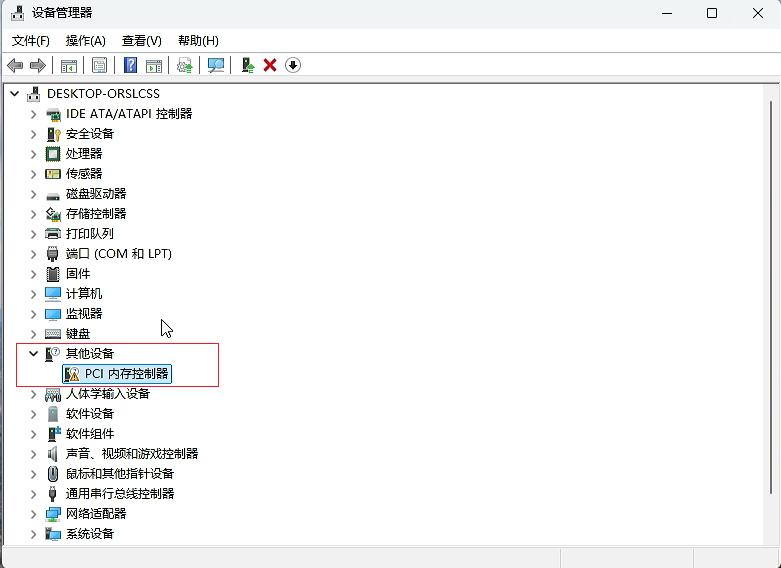

将程序固化到 flash 内,把开发板插入电脑 PCIE 卡槽,开机。打开设备管理器,可识别到 PCIE 设备。

Win 下能弹出该设备即可。

—Dubbo Provider处理服务调用请求源码)

![6-Django项目实战-[dtoken]-用户登录模块](http://pic.xiahunao.cn/6-Django项目实战-[dtoken]-用户登录模块)

![视觉图像处理中级篇 [2]—— 外观检查 / 伤痕模式的原理与优化设置方法](http://pic.xiahunao.cn/视觉图像处理中级篇 [2]—— 外观检查 / 伤痕模式的原理与优化设置方法)

战士:序)

】KNN算法与模型评估调优)