EDA断供危机下的冷思考:中国芯片设计软件的破局之道优雅草卓伊凡

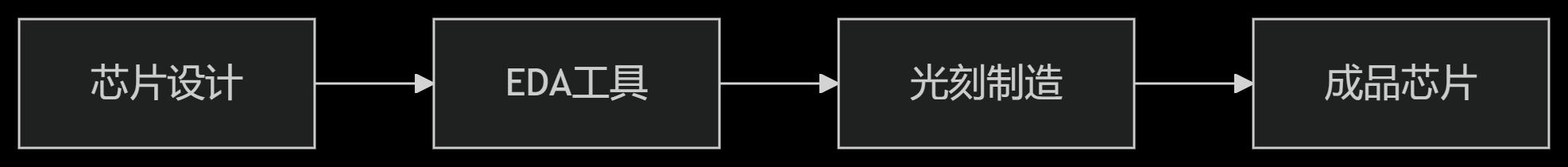

一、EDA是什么?芯片行业的”隐形基石”

1.1 EDA技术解析

EDA(Electronic Design Automation,电子设计自动化)是用于设计和验证集成电路的软件工具链,主要包括:

- 前端设计:逻辑设计、电路仿真(如Cadence Virtuoso)

- 后端实现:物理布局、布线(如Synopsys IC Compiler)

- 验证工具:DRC(设计规则检查)、LVS(版图对比)

1.2 国内EDA使用现状

| 指标 | 国际三巨头 | 国产EDA |

| 市占率 | 90%+(Synopsys/Cadence/Mentor) | <10% |

| 工艺支持 | 3nm及以下 | 14nm主流,7nm在研 |

| 工具链完整度 | 全流程覆盖 | 点工具突破 |

| 生态绑定 | 与台积电/ASML深度协同 | 本土代工厂适配中 |

典型依赖场景:

某国产GPU设计企业若被断供Cadence工具:

- 现有设计文件可能无法打开

- 无法生成GDSII格式的掩膜版图

- 与台积电的PDK(工艺设计套件)兼容性断裂

二、三个比喻:理解EDA与芯片制造的关系

比喻1:EDA如建筑师的CAD软件

- 没有EDA ≈ 让建筑师手绘摩天大楼图纸

- 现实差距:现代芯片包含百亿级晶体管,相当于规划一座超大型城市的供水/供电/交通网络

比喻2:EDA如芯片的”编译器和调试器”

- 写C++需要Visual Studio → 设计芯片需要EDA

- 但EDA还要解决:

-

- 晶体管级的”内存泄漏”(漏电流优化)

- 纳米级的”多线程冲突”(信号串扰)

比喻3:EDA生态如手机操作系统

- Android/iOS 需要开发者适配 → EDA 需要代工厂提供PDK

- 台积电的3nm PDK只完整支持Synopsys工具链,如同某些APP仅限iOS

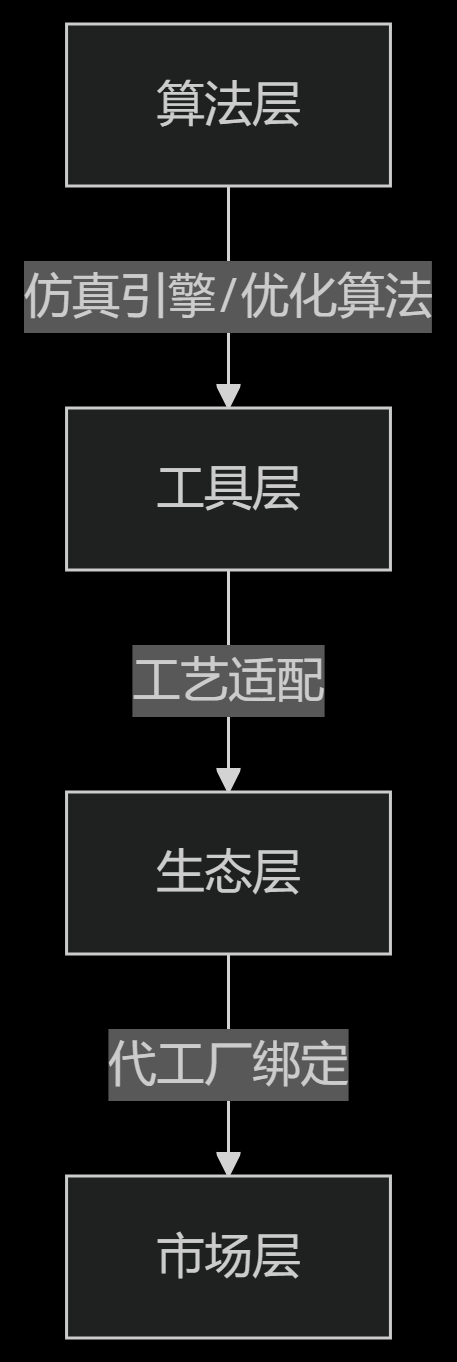

三、国产EDA的突围难点

3.1 技术壁垒金字塔

- 算法层:

-

- 电磁场求解器需要计算数学突破

- 时序分析依赖图论算法优化

- 生态层:

-

- 中芯国际的PDK对国产EDA支持度不足

- 设计师习惯国际工具(学习成本阻碍迁移)

3.2 数据对比:国内外研发投入

| 公司 | 年度研发费用 | EDA相关专利 |

| Synopsys | 15亿美元 | 2.3万+ |

| 华大九天 | 1.2亿美元 | 800+ |

| 概伦电子 | 0.8亿美元 | 300+ |

四、卓伊凡的核心观点:营商环境>技术本身

4.1 历史教训:为什么过去国产EDA起不来?

- 市场端:

-

- 芯片设计公司不敢用国产工具(担心影响流片)

- 代工厂优先服务国际EDA客户

- 政策端:

-

- 专项经费”撒胡椒面”,缺乏持续投入

- 知识产权保护不足,企业不愿共享工艺数据

4.2 杭州模式的启示

成功要素:

- 人才集聚:阿里系培养了大量基础软件人才

- 资本耐心:地方政府引导基金允许10年回报周期

- 场景开放:城市大脑等项目给国产软件试错机会

EDA需要:

- 中芯/长鑫等龙头开放PDK接口

- 政府采购强制国产EDA比例

- 建立芯片-EDA协同创新中心

结语:信心比黄金更重要

回顾历史:

- 1956年中国造不出晶体管 → 2023年长江存储实现232层NAND

- 2003年阿里云被嘲”忽悠” → 2023年亚太市场份额第一

卓伊凡坚信:

“EDA断供不是终点,而是国产基础软件的觉醒时刻。

只要守住三条底线——

- 让工程师体面生活(杜绝”造原子弹不如卖茶叶蛋”)

- 给企业试错空间(允许三年不盈利)

- 构建开放生态(芯片厂-EDA公司数据互通)

中国一定能长出自己的Synopsys。”

这不是技术问题,而是决心问题——当原创者的每一行代码都能获得尊重,当劳动者的每一滴汗水都能兑现价值,EDA的自主可控便水到渠成。

”)

)

——清晰题解)