好消息,好消息,小编最爱的国漫凡人修仙传电视剧版本的终于可以看了,小编我推荐一波啊,感兴趣的道友们可以去某酷视频去追剧啊。

好了,咱们言归正传啊。本期的案例是这个月中旬我们组的测试大哥阿永去某田实验室去测试我们的GMSL_poc 部分,在测试的时候发现很多路GMSL2的走线插损和回损都是不满足其限值要求的。于是阿永就给我电话说了一下这个情况,让我先帮忙做一下仿真看下情况,仿真的具体情况如下所示。

一,RX0_96712_FAKRA_1测试结果是不过的,目前可以优化的地方就是把POC电感的CUTOUT的H值加大即可,就是在POC电感下面多净空一层,挖空L6-L7六层,参考L5层。

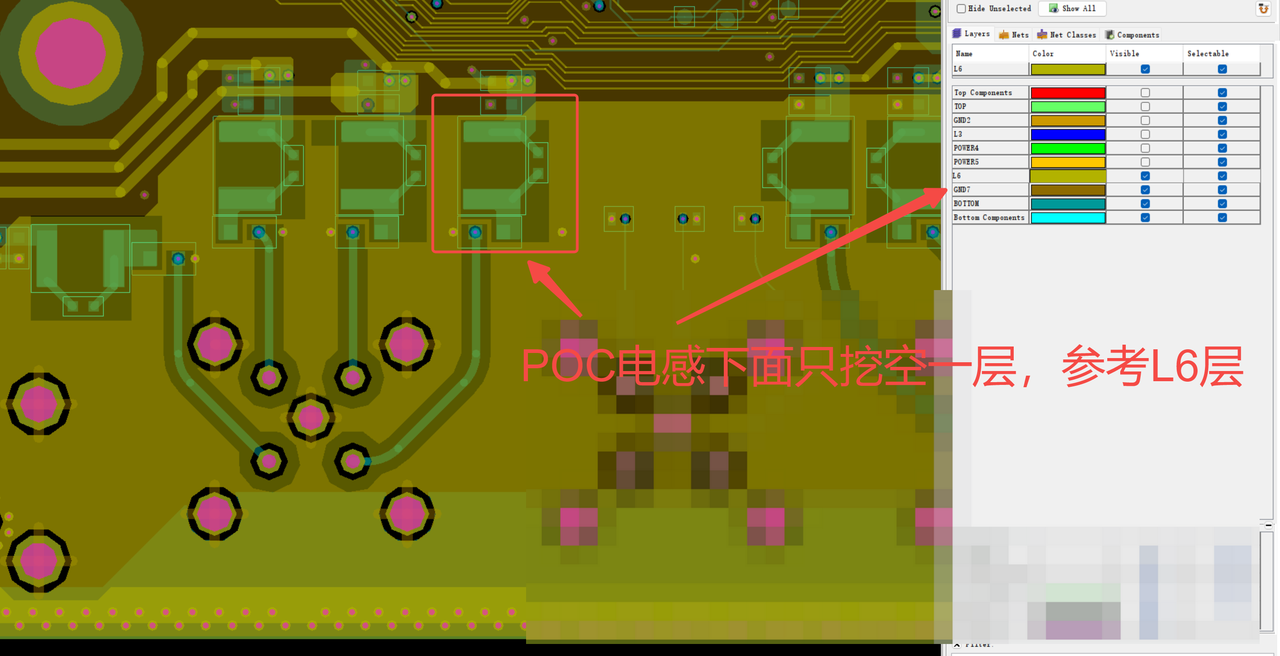

1,初始版本是POC电感下面挖空相邻一层L7,参考L6层。

(初始版本的PCB)

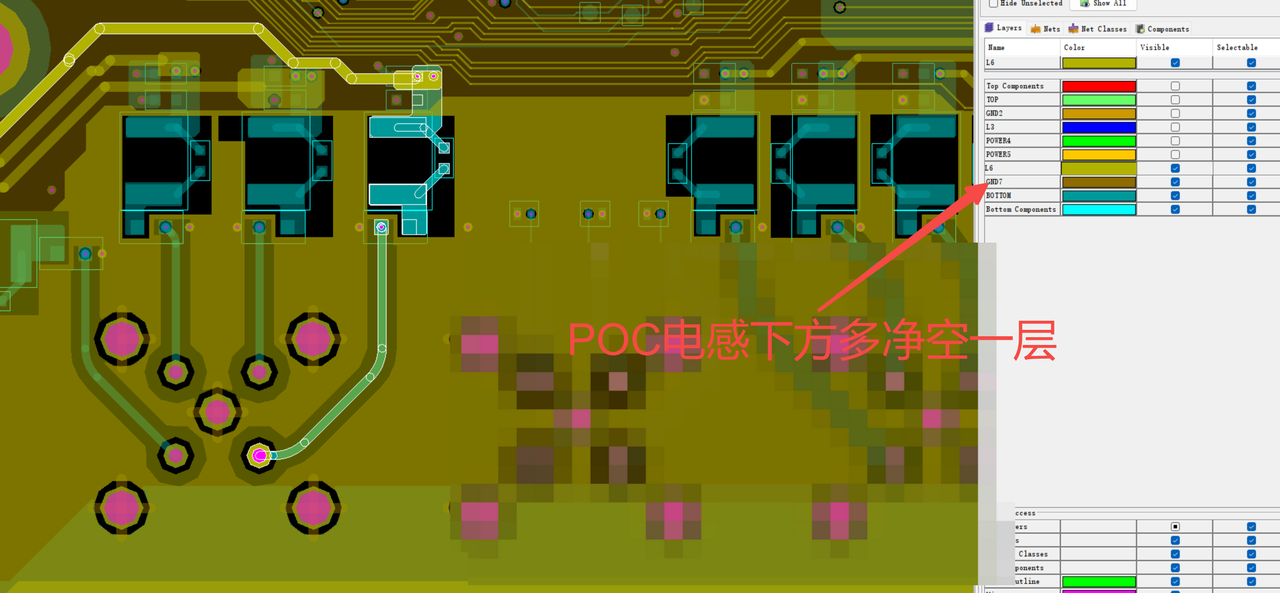

2,现在是改为POC电感下面挖空相邻的两层,即挖空L6,L7两层,参考L5层。

(优化后版本的PCB)

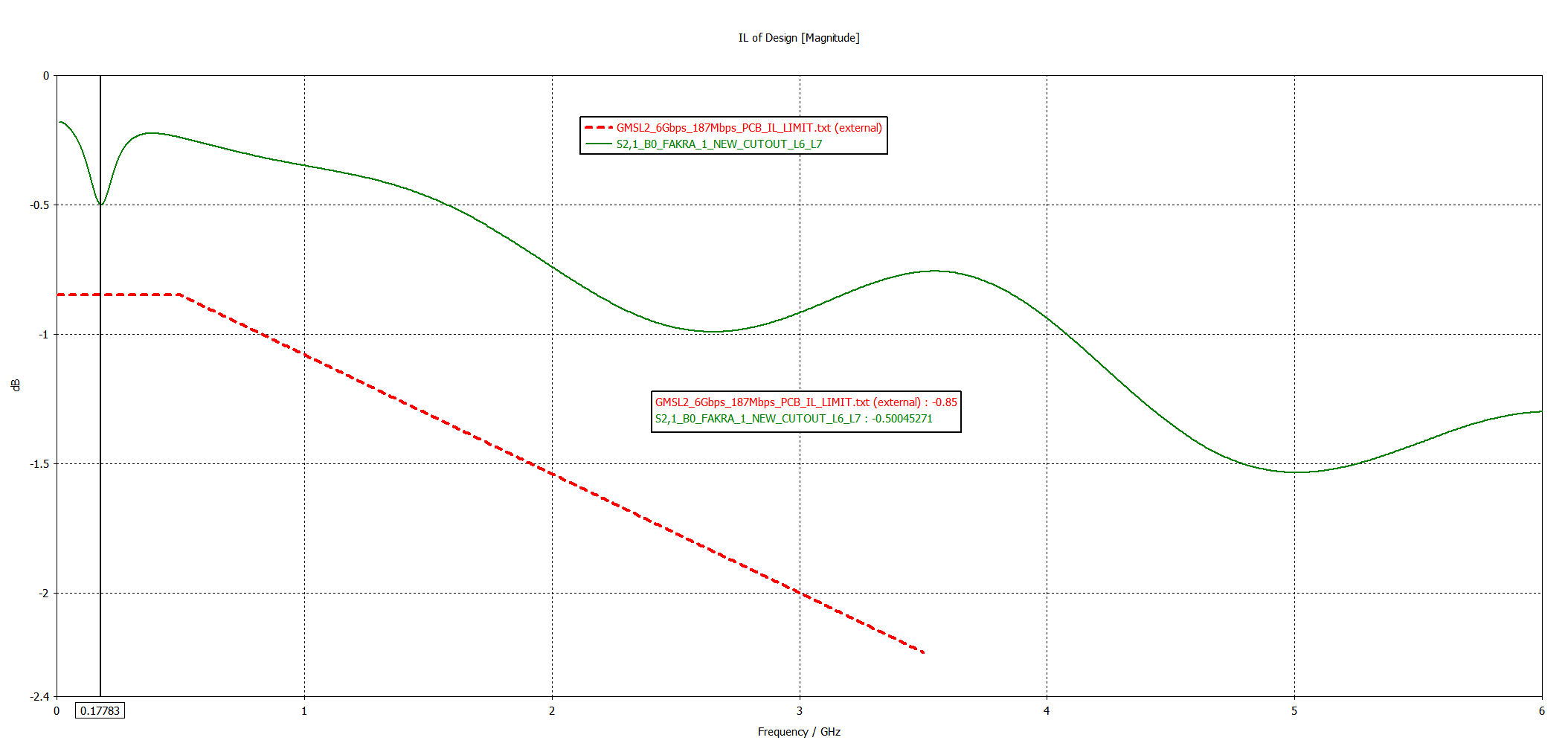

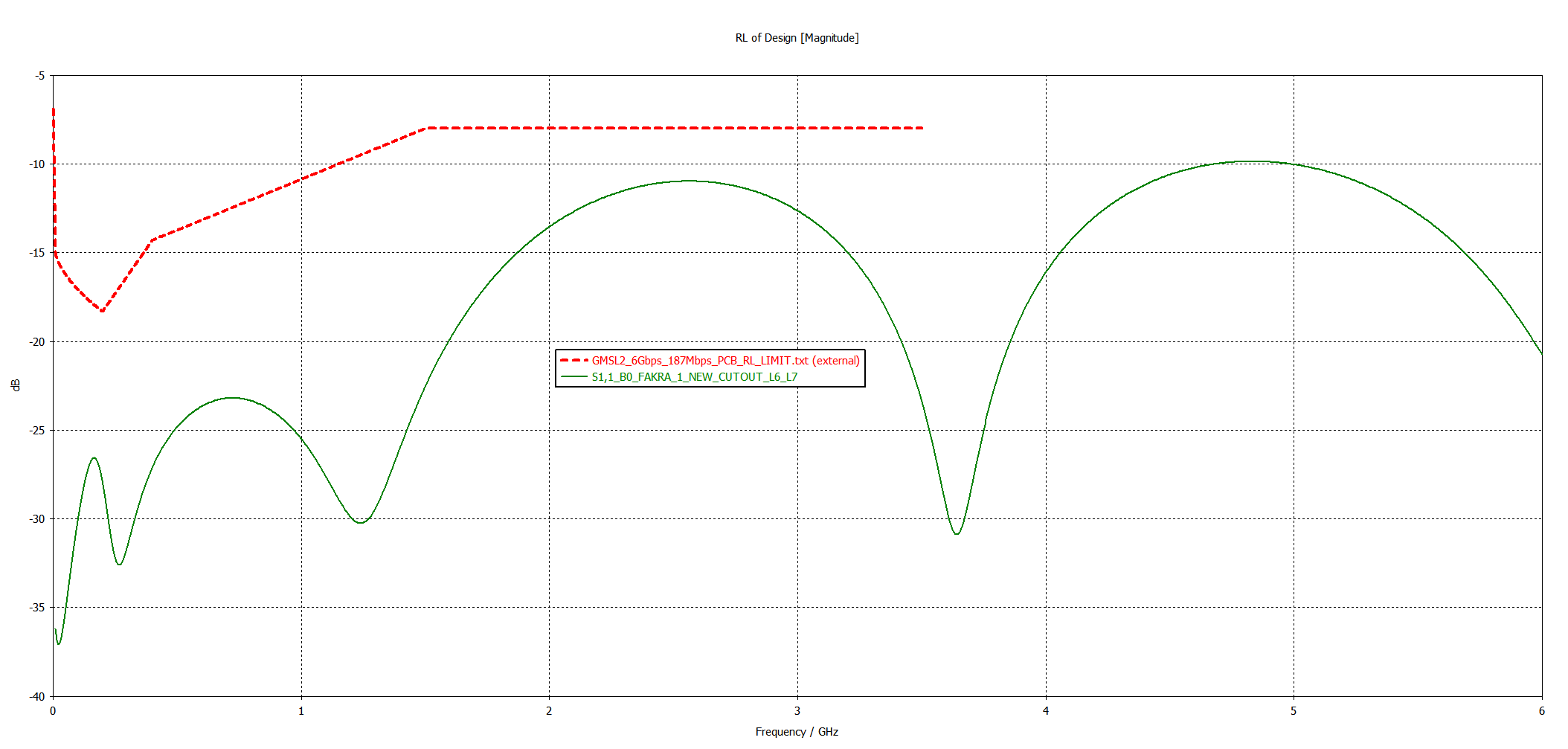

二,优化后看下其仿真效果:

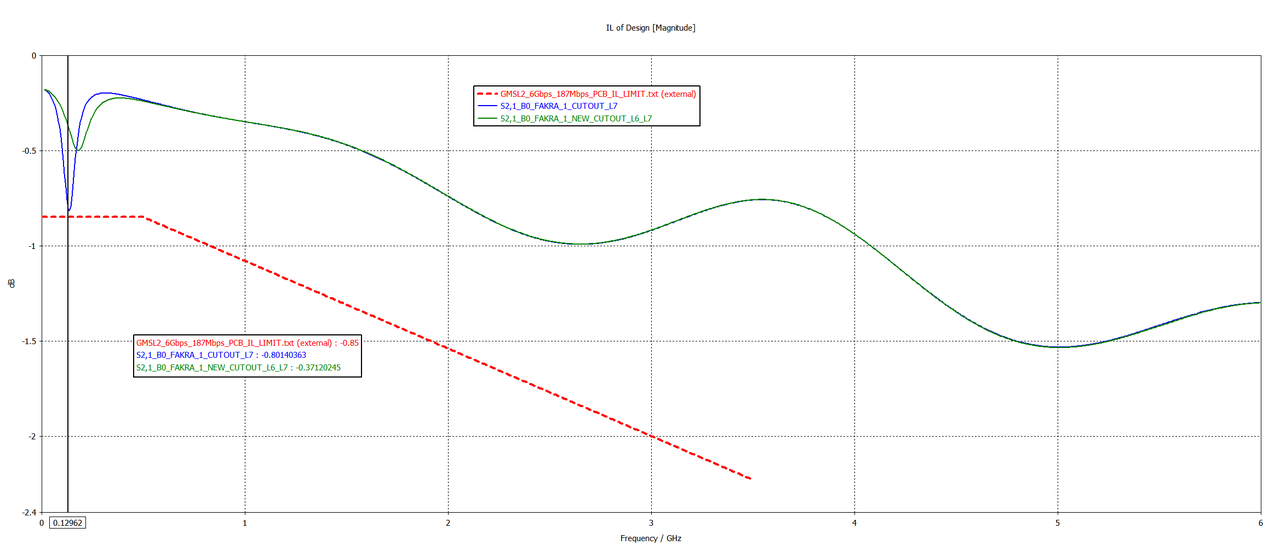

1, RX0_96712_FAKRA_1_S21:

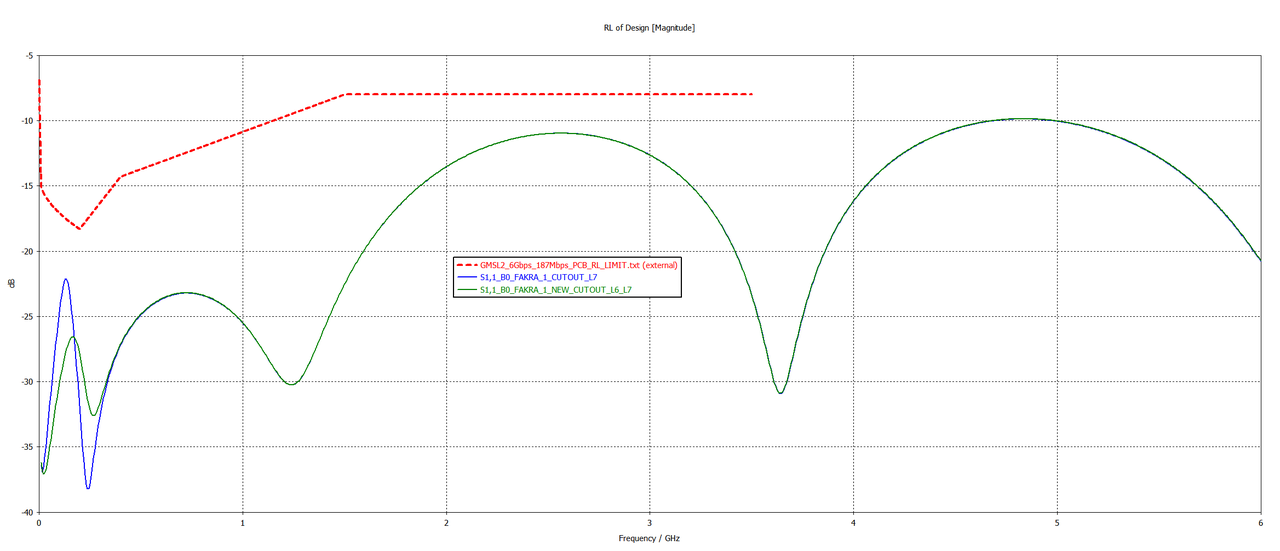

2, RX0_96712_FAKRA_1_S11:

3,RX0_96712_FAKRA_1_S21对比之前的版本:

4,RX0_96712_FAKRA_1_S11对比之前的版本:

三,若是测试的时候发现我们的GMSL走线在低频段的时候其S21插损是不能满足手册的限值要求,我们可以从以下几个方面去改善:

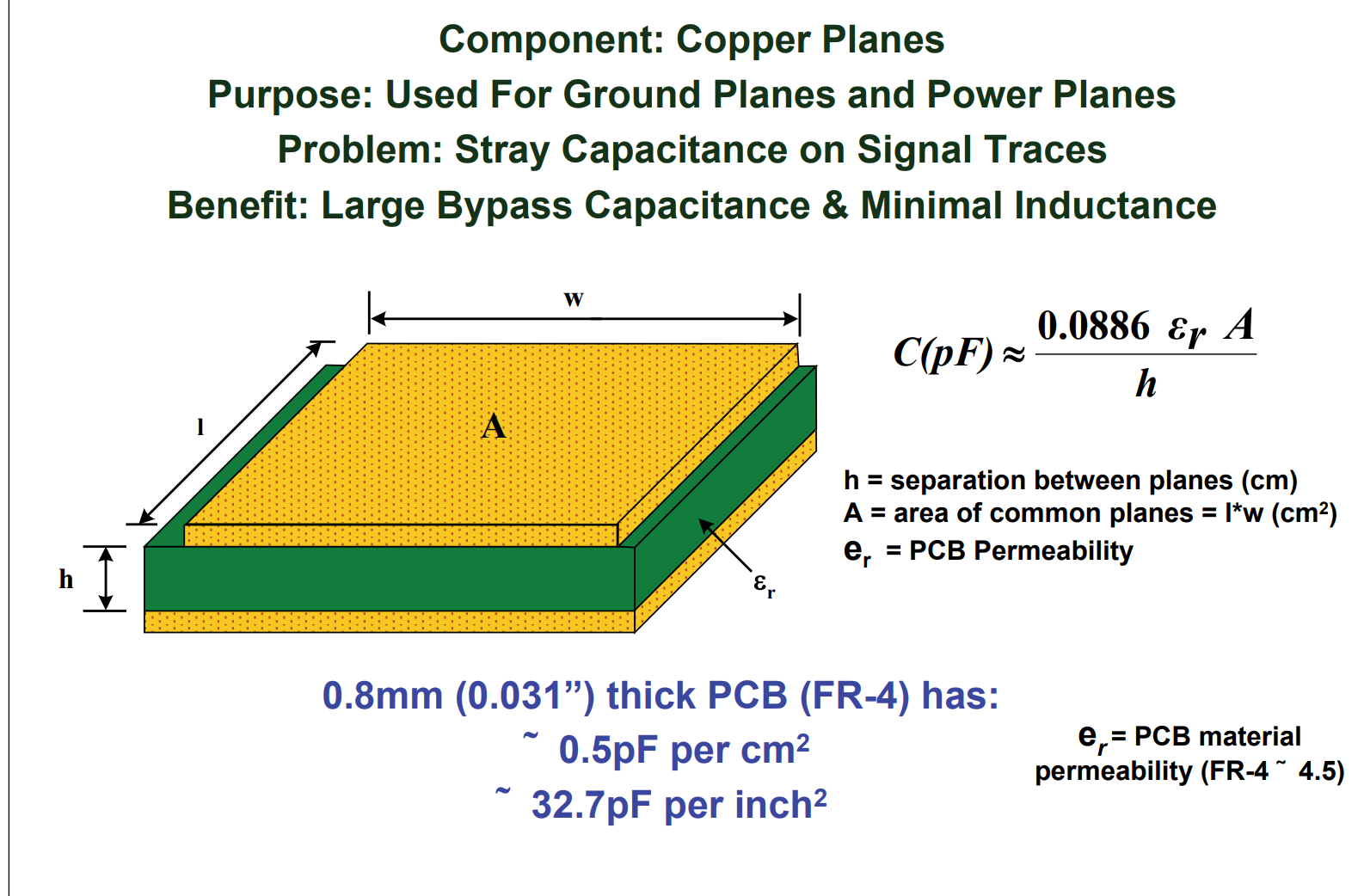

1,增加POC电感到其参考平面的距离H,即POC电感正下方在布线空间允许的情况下,多挖空几层。(主要是减少POC电感下面的寄生电容,因为寄生电容的引入,会导致POC电感在某些频段的阻抗性能严重下降,对信号的隔离效果也达不到设计要求,对信号的隔离效果也达不到设计要 求)

小编之前也有写过一遍文章专门讲解电感的Q值的:

Marin说PCB之Coilcraft&Bourns POC 电感的性能对比![]() https://blog.csdn.net/weixin_45223454/article/details/133828580

https://blog.csdn.net/weixin_45223454/article/details/133828580

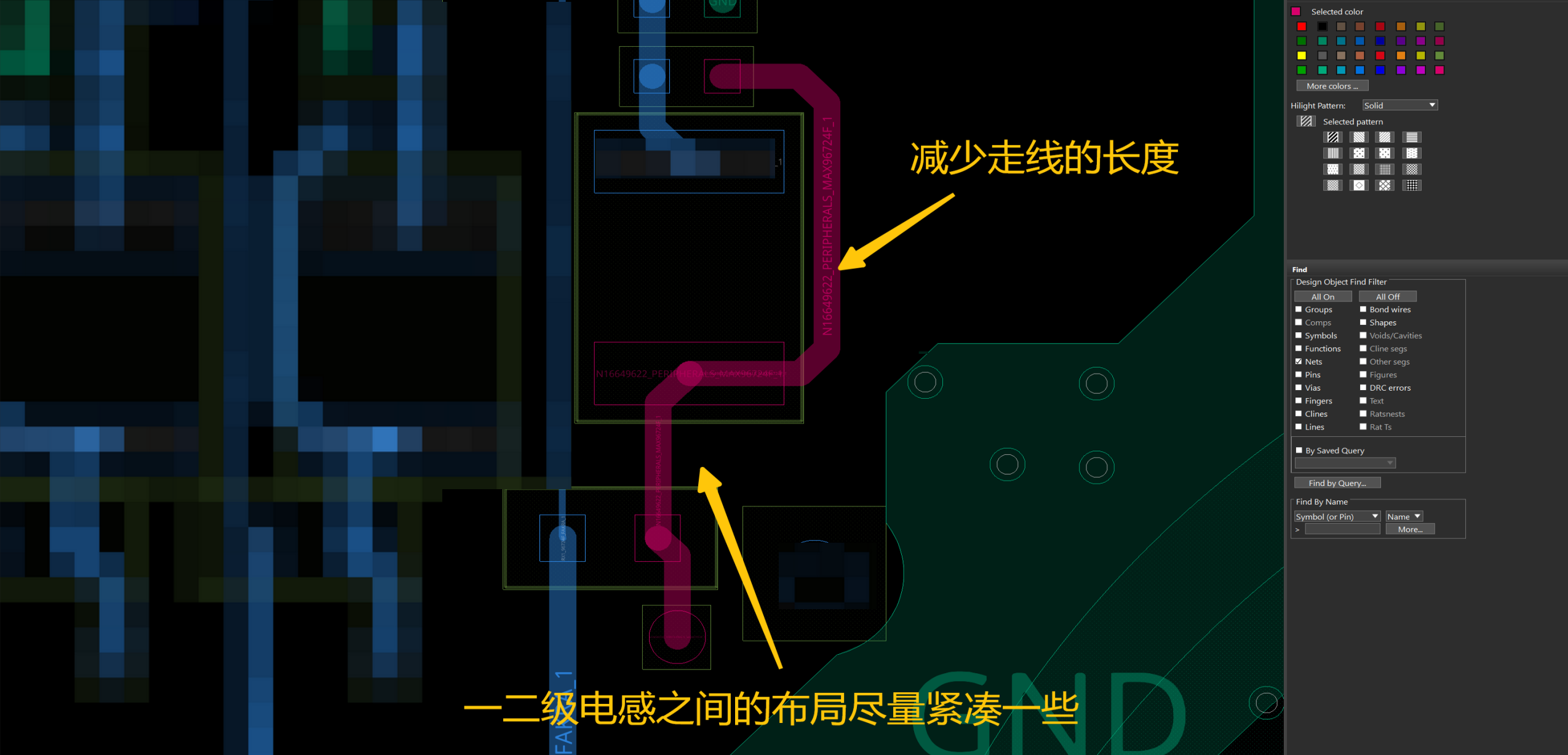

2,POC一二级电感之间的布局尽量紧凑,不要离的太远或者是有间隙,(主要就是减少铜皮的面积A)

3,二级电感上并联的电阻尽量并排和电感摆放,与其电感的走线也要尽量短一些,减少其寄生参数对GMSL2的插损性能的影响。

4,挖空相邻的GND层面的时候,注意检查一下POC器件层的走线是否有投影在这个挖空区域内,尽量避免这个情况出现。

5,增加POC电感的挖空尺寸,挖空的尺寸还是参考之前要求:挖空区域的宽度≥1.75倍(ratio值)的pad宽度为宜, ratio值具体要视pad 的尺寸、设计的叠构和信号要求(tr)而定。

6, 尽量减少POC电感上的走线或者是铺铜皮的宽度,在满足其载流的前提下。(主要就是减少铜皮的面积A)

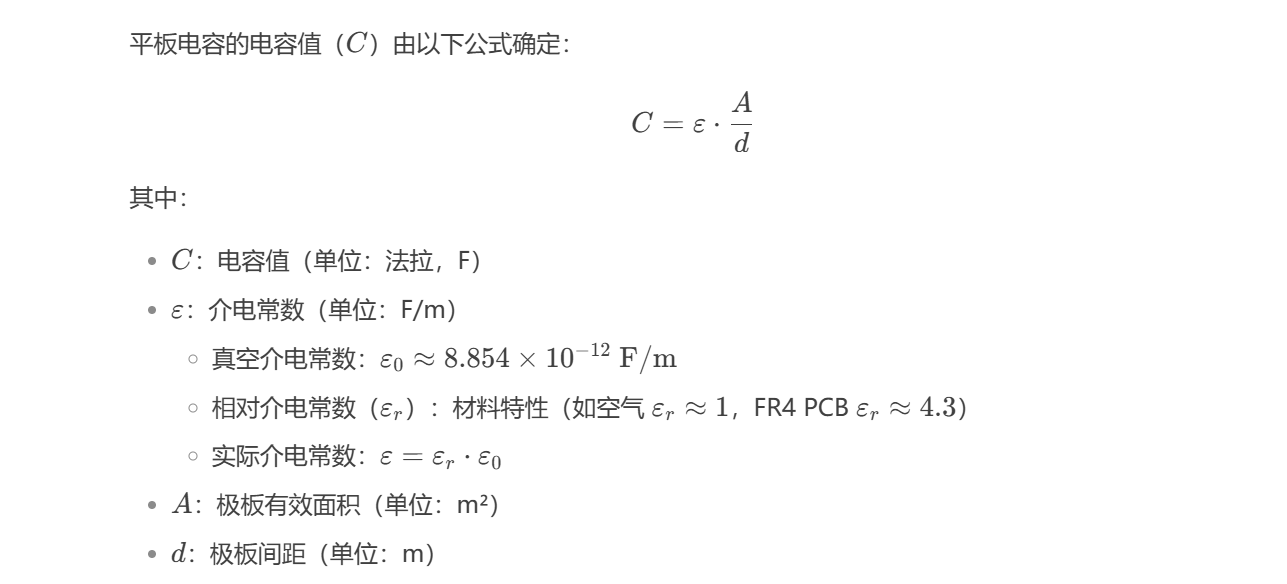

7, 使用相对介电常数更低的板材,这样也可以减少POC电感下面的寄生电容。但是这个建议不太实用,因为板材一般在PCB设计前期的时候就差不多定下来了,不太可能因为这个减少走线上的寄生电容就去改板材的,这只是一个使用建议之一,小编我个人感觉不太实用的,也不推荐的。

好了,诸位道友们以上就是本期的所有内容了,我们下期文章不见不散。

--------声明:本文属于小编的原创文章,如需转载请注明来源!