一、概述

(一)QSPI 简介

QSPI(Quad Serial Peripheral Interface)是一种高速串行通信接口,在标准 SPI(Serial Peripheral Interface)的基础上扩展至 4 条数据线(Quad Mode),显著提升数据传输速率。它广泛应用于 Flash 存储器、传感器和微控制器之间的通信。

(二)主要特性

多种模式支持 :兼容 Standard SPI(1 - bit 模式)、Dual SPI(2 - bit 模式)以及 Quad SPI(4 - bit 模式,最高吞吐量)。

高时钟频率 :通常支持 50MHz - 133MHz(取决于芯片),为数据传输提供高速时钟保障。

低引脚占用 :仅需 6 个引脚(CLK, CS, IO0 - IO3)即可实现全双工通信,有效节省硬件资源。

内存映射模式(XIP, Execute - In - Place) :允许 CPU 直接访问 QSPI Flash,无需额外缓存,提升系统运行效率。

(三)应用场景

在嵌入式系统中,QSPI 常用于连接微控制器与外部 Flash 存储器,实现程序代码和数据的高速读写操作;还可与各类传感器配合,快速传输传感器采集到的数据,满足工业控制、汽车电子、物联网等诸多领域的实时性与大数据量传输需求。

二、AS32A601 QSPI 硬件设计

| 引脚名称 | 功能 | 说明 |

| CLK | 时钟信号 | 主设备输出,从设备同步数据 |

| CS | 片选信号(低电平有效) | 使能从设备通信 |

| IO0 (DQ0) | 数据线0(MOSI in SPI模式) | 单线模式:单向数据输入/输出 |

| IO1 (DQ1) | 数据线1(MISO in SPI模式) | 单线模式:单向数据输入/输出 |

| IO2 (DQ2) | 数据线2(WP# in SPI模式) | Quad模式:双向数据传输 |

| IO3 (DQ3) | 数据线3(HOLD# in SPI模式) | Quad模式:双向数据传输 |

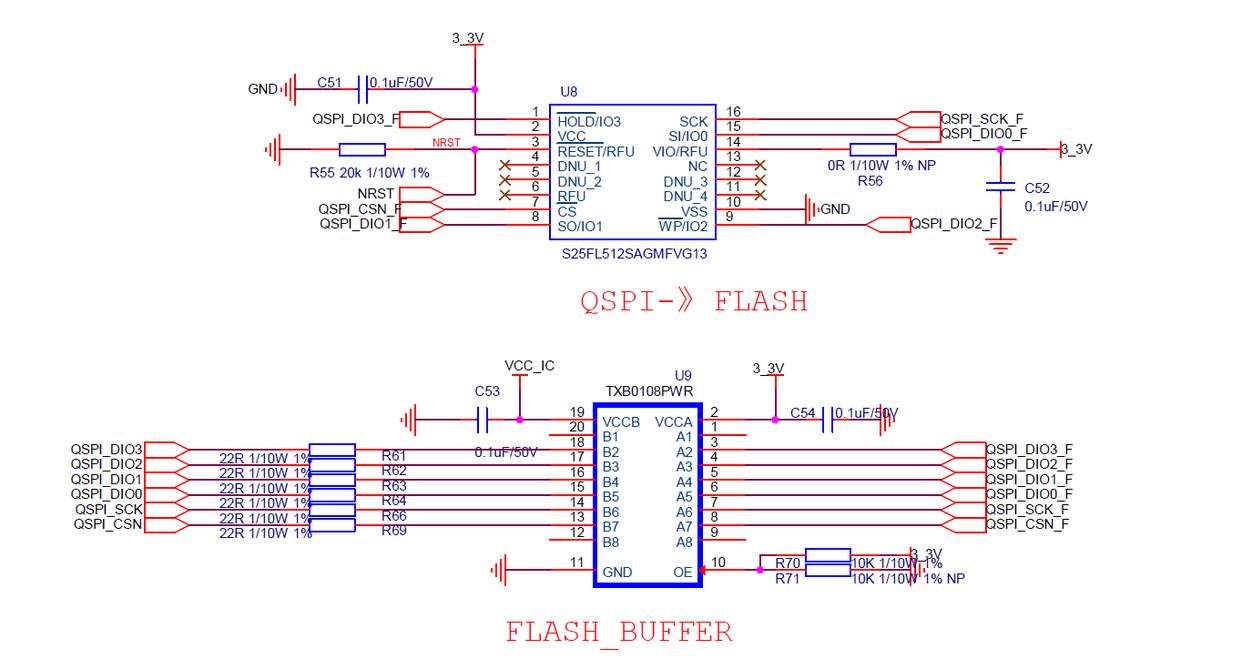

(二)开发板配置

在 AS32A601 开发板上,QSPI 经过一个 BUFFER 芯片接入 QSPI_FLASH,所选 FLASH 型号为 S25FL512SAGMFVG13,该型号 QSPI 支持最大速率可达 45MHz,为系统稳定运行提供可靠存储支持。

三、QSPI 时序解析

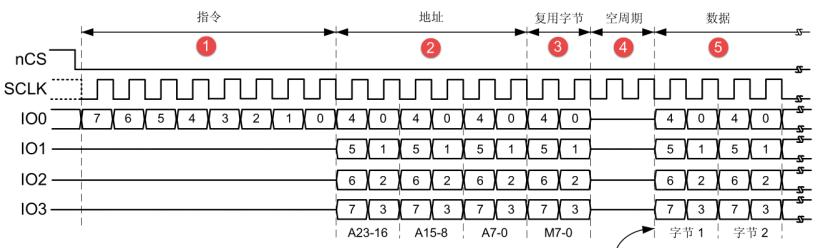

(一)指令阶段

这一阶段,将在QSPI_CCR[7:0]寄存器的instruction字段中配置的一条8位指令发送到Flash,指定待执行操作的类型。

尽管大多数Flash从IO0/SO信号(单线SPI模式)只能以一次1位的方式接收指令,但指令阶段可选择一次发送2位(在双线SPI模式中通过IO0/IO1)或一次发送4位(在四线SPI模式中通过IO0/IO1/IO2/IO3)。这可通过QSPI_CCR[9:8]寄存器中的IMODE[1:0]字段进行配置。若IMODE = 00,则跳过指令阶段,命令序列从地址阶段(如果存在)开始。

(二)地址阶段

在地址阶段,将1-4字节发送到Flash,指示操作地址。待发送的地址字节数在QSPI_CCR[13:12]寄存器的ADSIZE[1:0]字段中进行配置。在间接模式和自动轮询模式下,待发送的地址字节在QSPI_AR寄存器的ADDRESS[31:0]中指定;在内存映射模式下,则通过AHB(来自于内核或DMA)直接给出地址。地址阶段可一次发送1位(单线SPI模式通过SO)、2位(双线SPI模式中通过IO0/IO1)或4位(在四线SPI模式中通过IO0/IO1/IO2/IO3)。这可通过QUADSPI_CCR[11:10]寄存器中的ADMODE[1:0]字段进行配置。若ADMODE = 00,则跳过地址阶段,命令序列直接进入下一阶段(如果存在)。

(三)交替字节阶段

在交替字节阶段,将1-4字节发送到Flash,一般用于控制操作模式。待发送的交替字节数在QSPI_CCR[17:16]寄存器的ABSIZE[1:0]字段中进行配置。待发送的字节在QSPI_ABR寄存器中指定。

交替字节阶段可一次发送1位(在单线SPI模式中通过SO)、2位(在双线SPI模式中通过IO0/IO1)或4位(在四线SPI模式中通过IO0/IO1/IO2/IO3)。这可通过QSPI_CCR[15:14]寄存器中的ABMODE[1:0]字段进行配置。若ABMODE = 00,则跳过交替字节阶段,命令序列直接进入下一阶段(如果存在)。

交替字节阶段存在仅需发送单个半字节而不是一个全字节的情况,比如采用双线模式并且仅使用两个周期发送交替字节时。在这种情况下,固件可采用四线模式(ABMODE = 11)并发送一个字节,方法是ALTERNATE的位7和3置“1”(IO3保持高电平)且位6和2置“0”(IO2线保持低电平)。此时,半字节的高2位存放在ALTERNATE的位4:3,低2位存放在位1和0中。例如,如果半字节2 (0010)通过IO0/IO1发送,则ALTERNATE应设置为0x8A (1000_1010)。

(四)空指令周期阶段

在空指令周期阶段,给定的1-31个周期内不发送或接收任何数据,目的是当采用更高的时钟频率时,给Flash留出准备数据阶段的时间。这一阶段中给定的周期数在QSPI_CCR[22:18]寄存器的DCYC[4:0]字段中指定。在SDR和DDR模式下,持续时间被指定为一定个数的全时钟周期。若DCYC为零,则跳过空指令周期阶段,命令序列直接进入数据阶段(如果存在)。空指令周期阶段的操作模式由DMODE确定。为确保数据信号从输出模式转变为输入模式有足够的“周转”时间,使用双线和四线模式从Flash接收数据时,至少需要指定一个空指令周期。

(五)数据阶段

在数据阶段,可从Flash接收或向其发送任意数量的字节。在间接模式和自动轮询模式下,待发送/接收的字节数在QSPI_DLR寄存器中指定。在间接写入模式下,发送到Flash的数据必须写入QSPI_DR寄存器。在间接读取模式下,通过读取QSPI_DR寄存器获得从Flash接收的数据。在内存映射模式下,读取的数据通过AHB直接发送回Cortex或DMA。数据阶段可一次发送/接收1位(在单线SPI模式中通过SO)、2位(在双线SPI模式中通过IO0/IO1)或4位(在四线SPI模式中通过IO0/IO1/IO2/IO3)。这可通过QUADSPI_CCR[15:14]寄存器中的ABMODE[1:0] 字段进行配置。若DMODE = 00,则跳过数据阶段,命令序列在拉高nCS时立即完成。这一配置仅可用于仅间接写入模式。

四、QSPI 与 SPI 异同比较

QSPI(Quad SPI)和SPI(Serial Peripheral Interface)是两种串行通信协议,用于在主设备和从设备之间进行数据传输。它们有一些相似之处,但也有一些重要的区别。

(一)相似之处

串行通信本质 :二者均为串行通信协议,通过少量引脚实现数据传输,在硬件资源有限的场景下具有显著优势。

主从架构 :均基于主从结构,主设备主导通信发起与时序控制,从设备依主设备指令响应并完成数据交互,便于系统级的设备管理和任务调度。

(二)不同之处

传输速率差异 :QSPI 凭借四条数据线(Quad 模式)可同时传输四个数据位,支持更高传输速率;SPI 通常仅使用一条数据线,每次仅能传输一个数据位,传输速率相对较低。

总线模式多样性 :QSPI 支持单线、双线、四线等多种总线模式,可根据应用场景灵活选择;SPI 一般仅支持单线模式,难以满足对高带宽有需求的复杂应用。

时钟频率范围 :QSPI 为匹配高速数据传输,通常支持更高时钟频率;SPI 的时钟频率设计相对较低,适用于对实时性要求不苛刻的场景。

引脚占用情况 :QSPI 为实现四线模式高速数据传输,需更多引脚;SPI 仅需少量引脚即可完成基本通信功能,在简单应用中硬件连接更为简便。

片选信号运用 :QSPI 与 SPI 均使用片选信号(Chip Select)选择通信从设备,但在复杂多设备系统中,QSPI 的多线模式可减少总线切换次数,提升整体通信效率。

总之,需要根据具体的应用需求和设备支持来选择使用QSPI还是SPI。QSPI适用于需要更高传输速率和更大带宽的应用,而SPI适用于传输速率要求不高的应用。

)

)