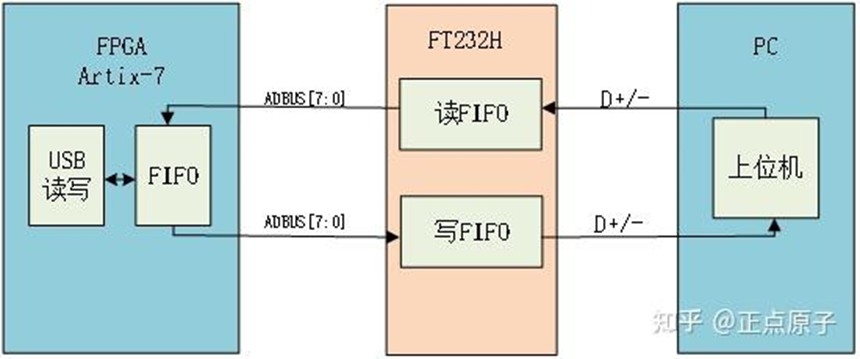

FT232H是一个单通道USB 2.0高速(480Mb/s)转换为UART/FIFO IC,具有多种工业标准串行或并行接口配置能力。

1.实验板卡

FPGA型号:

FT232H型号:

FT232H SINGLE CHANNEL HI-SPEED USB TO MULTIPURPOSE UART/FIFO IC Datasheet

Version 2.0

2.数据手册说明

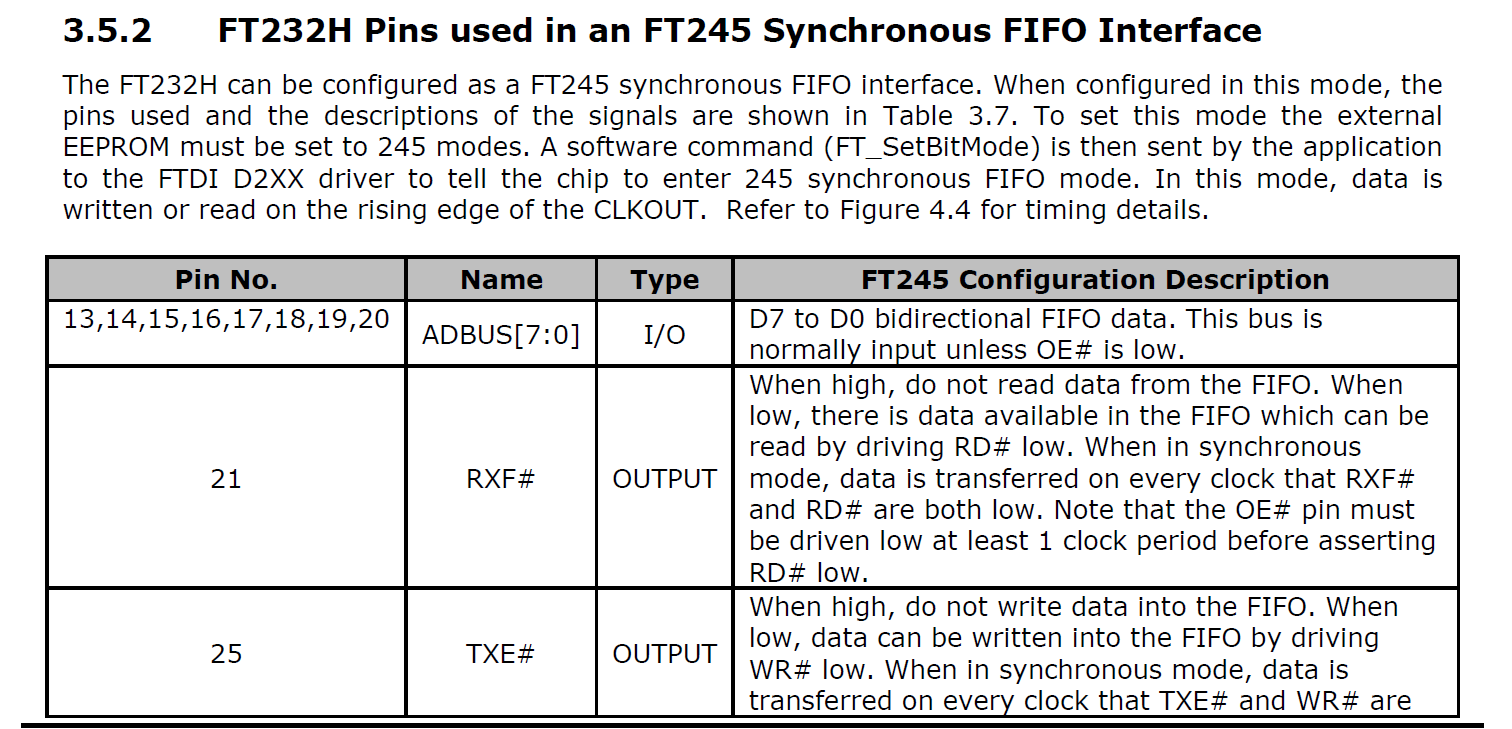

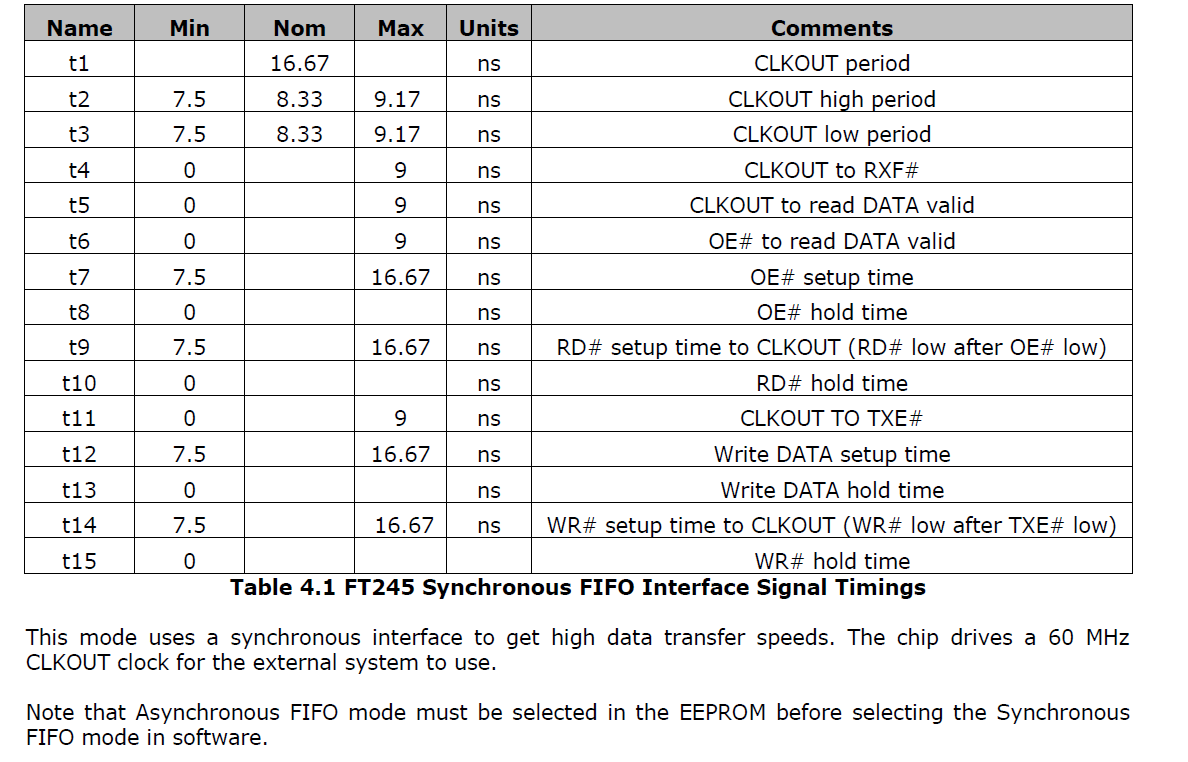

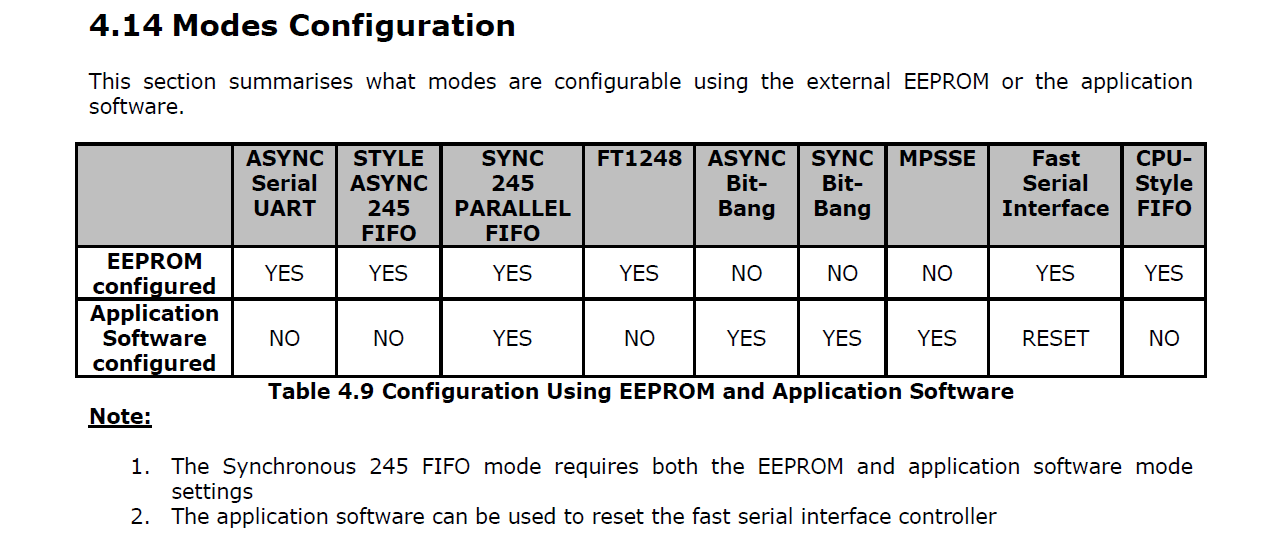

选择的是同步fifo模式。上面是管脚信号说明。

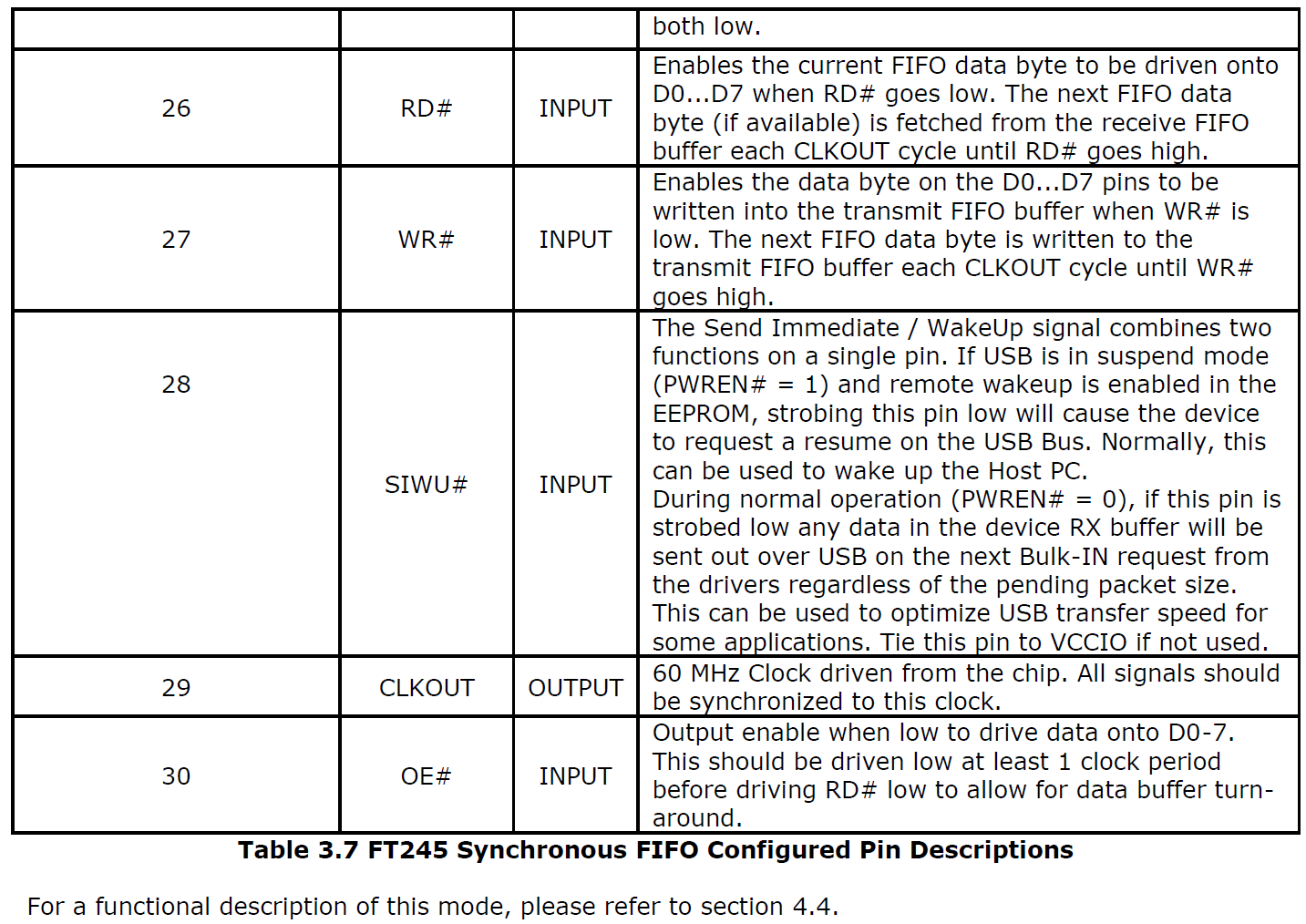

以上是读写时序

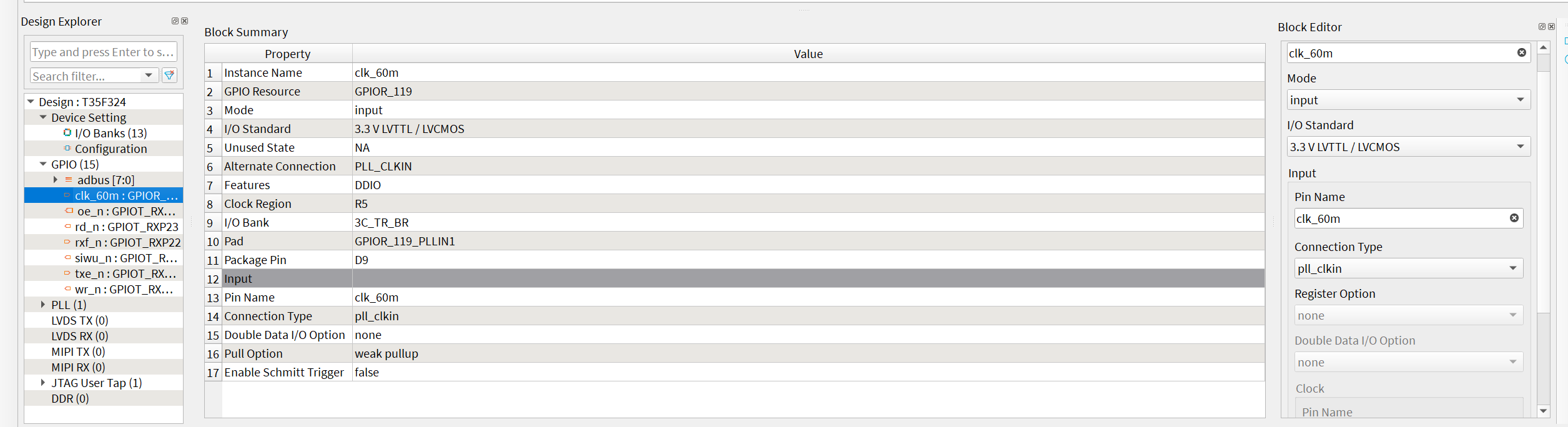

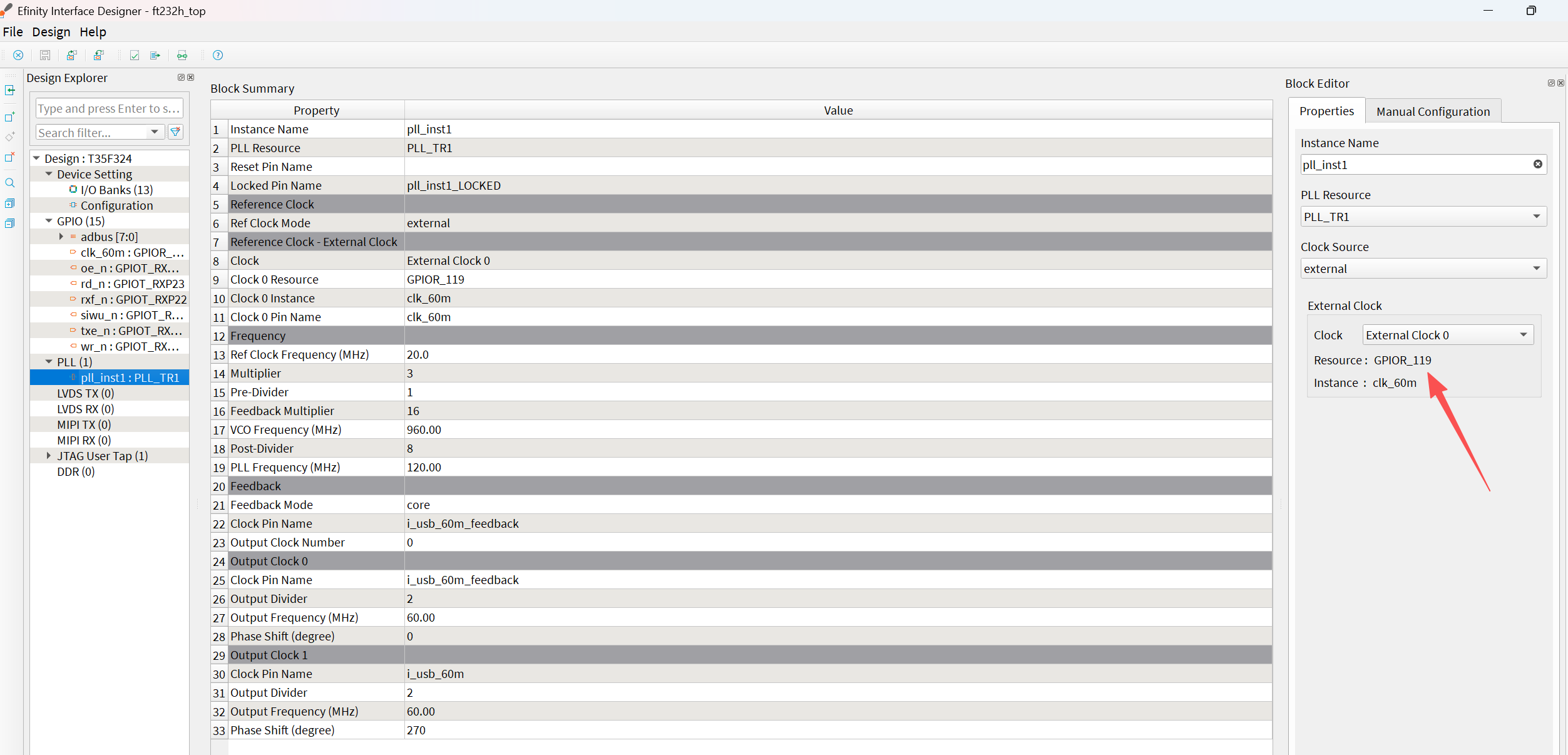

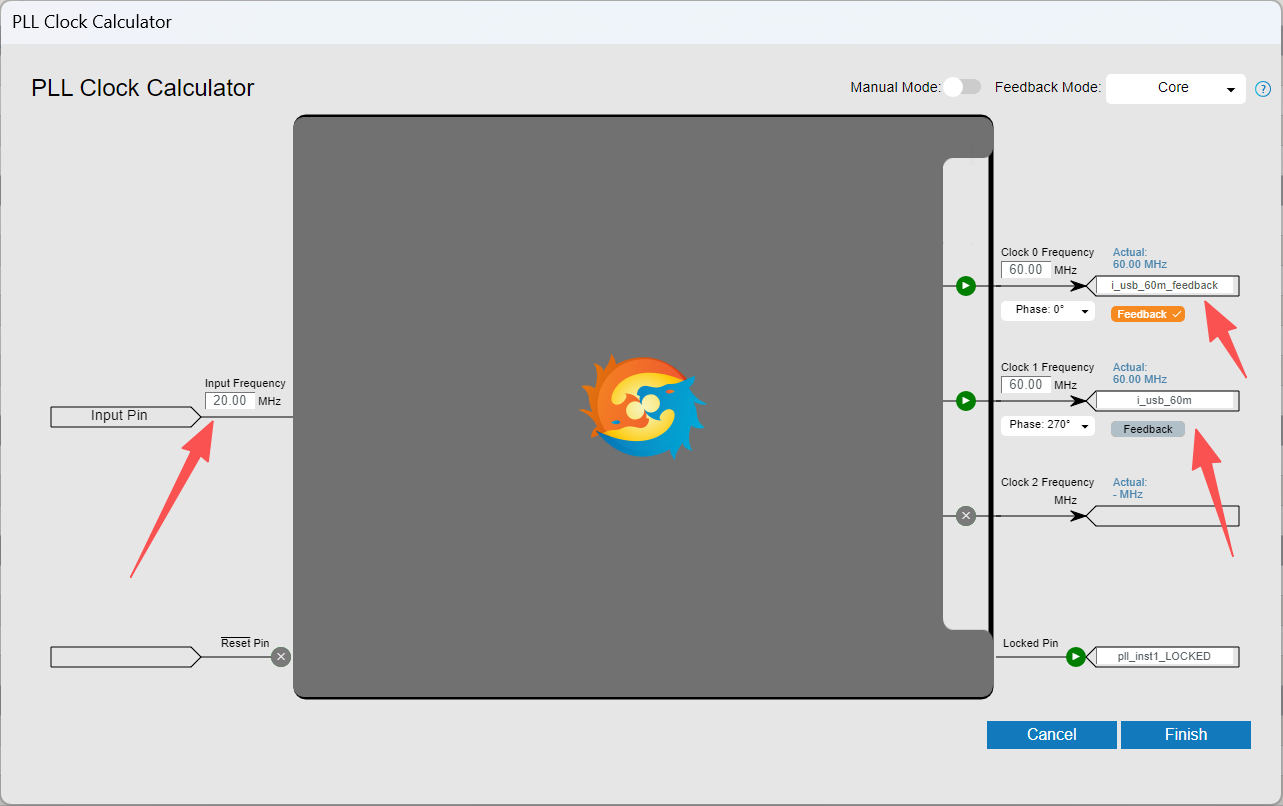

注意这里的时钟周期是60mhz,我用的是FPGA上的PLL输出的60m的时钟,因为如果要用FT232H输出的时钟的话,需要对EEPROM进行配置,配置成FIFO模式,再通过上位机发送同步指令才可以输出60MHZ时钟。

时钟周期等于16.67 ns,也就是时钟频率是1/T=1/16.67ns=1/1.67*10^(-9),结果约等于60MHZ。

FT232配置见:FPGA外接FT232H配置FIFO实现USB通信回环测试-CSDN博客

3.代码设计

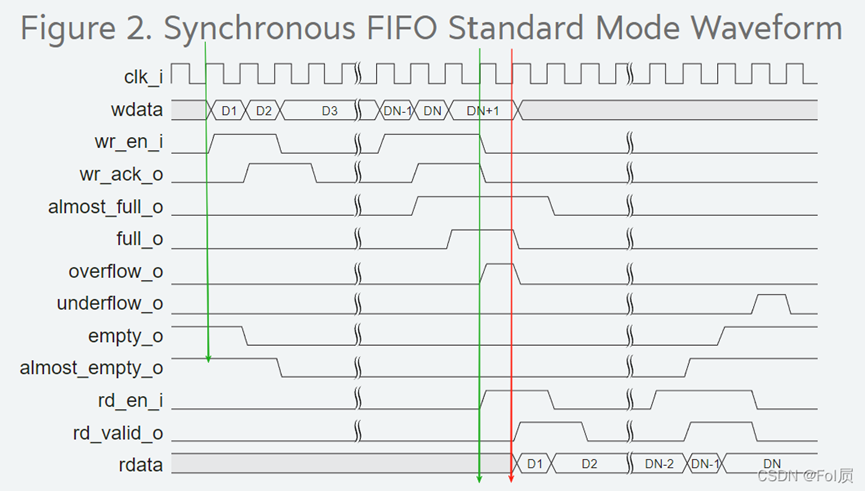

FPGA中FIFO IP的时序。写的时候写使能和数据是同步的,读出数据的时候,读出的数据延迟读使能信号一个周期。

3.1 ft232h_top

module ft232h_top(/////////////////////////////debuginput jtag_inst1_CAPTURE ,input jtag_inst1_DRCK ,input jtag_inst1_RESET ,input jtag_inst1_RUNTEST ,input jtag_inst1_SEL ,input jtag_inst1_SHIFT ,input jtag_inst1_TCK ,input jtag_inst1_TDI ,input jtag_inst1_TMS ,input jtag_inst1_UPDATE ,output jtag_inst1_TDO ,/////////////////////////////////input i_usb_60m ,//input reset ,input rxf_n ,input txe_n ,output rd_n ,output wr_n ,output siwu_n ,output oe_n , //oe_n:0,FT232h数据输出;oe_n:1,FPGA数据输入到FT232中去 input [7:0] data_in ,output [7:0] data_out ,output [7:0] data_out_oe );wire empty;

wire [7:0]data_wr;

wire wr_fifo;

wire rst_busy;

wire full;

wire [7:0] data_rd;

wire reset ;

wire [7:0]data_count;

wire rd_fifo_flag_r;

wire rd_fifo_flag;assign siwu_n=1'b1; //用于唤醒主机电脑fifo u_fifo(

.full_o ( full ),

.empty_o ( empty ),

.rdata ( data_rd ),

.clk_i ( i_usb_60m ),

.wr_en_i ( wr_fifo ),

.rd_en_i ( rd_fifo ),

//.a_rst_i ( vio_reset_n ),

.a_rst_i ( reset ),

.wdata ( data_wr ),

.datacount_o ( data_count ),

.rst_busy ( ) //高电平有效,高电平复位

);ft232h_send ft232h_send_inst(.clk_60m (i_usb_60m) ,//.reset (vio_reset_n) ,.reset (reset) ,.rxf_n (rxf_n) , .data_in (data_in) , .wr_n (wr_n),.rd_n (rd_n) , .oe_n (oe_n) , .empty_o (empty) ,.full_o (full) ,//.rst_busy (rst_busy) ,.data_wr (data_wr) , .wr_fifo (wr_fifo)

);ft232h_recv ft232h_recv_inst(.clk_60m (i_usb_60m) ,//.reset (vio_reset_n) ,.reset (reset) ,.txe_n (txe_n),.rd_n (rd_n),.oe_n (oe_n),.rxf_n (rxf_n),.wr_fifo (wr_fifo),.wr_n (wr_n),.data_out (data_out),.data_out_oe(data_out_oe),//.rst_busy (rst_busy),.data_count (data_count),.full_o (full),.empty_o (empty) ,.data_rd (data_rd) ,.rd_fifo (rd_fifo) ,.rd_fifo_flag_r (rd_fifo_flag_r),.rd_fifo_flag (rd_fifo_flag)

);edb_top edb_top_inst (.bscan_CAPTURE ( jtag_inst1_CAPTURE ),.bscan_DRCK ( jtag_inst1_DRCK ),.bscan_RESET ( jtag_inst1_RESET ),.bscan_RUNTEST ( jtag_inst1_RUNTEST ),.bscan_SEL ( jtag_inst1_SEL ),.bscan_SHIFT ( jtag_inst1_SHIFT ),.bscan_TCK ( jtag_inst1_TCK ),.bscan_TDI ( jtag_inst1_TDI ),.bscan_TMS ( jtag_inst1_TMS ),.bscan_UPDATE ( jtag_inst1_UPDATE ),.bscan_TDO ( jtag_inst1_TDO ),.la0_clk ( i_usb_60m ),.la0_rxf_n ( rxf_n ),.la0_txe_n ( txe_n ),.la0_rd_n ( rd_n ),.la0_wr_n ( wr_n ),.la0_oe_n ( oe_n ),.la0_data_in ( data_in ),.la0_data_out ( data_out ),.la0_data_out_oe ( data_out_oe ),.la0_siwu_n ( siwu_n ),.la0_reset ( reset ),.la0_data_wr ( data_wr ),.la0_empty ( empty ),.la0_full ( full ),.la0_wr_fifo ( wr_fifo ),.la0_data_rd ( data_rd ),.la0_rd_fifo ( rd_fifo ),.la0_data_count (data_count),.la0_rd_fifo_flag_r (rd_fifo_flag_r ),.la0_rd_fifo_flag (rd_fifo_flag ),.vio0_clk ( i_usb_60m ),.vio0_data_in ( data_in ),.vio0_data_out ( data_out ),.vio0_data_out_oe ( data_out_oe ),.vio0_reset ( reset )

);endmodule3.2 ft232h_send

//读出FT232H的值,也就是驱动FT232H发送数据,

module ft232h_send(input clk_60m ,input reset ,input rxf_n , //FT232h输出的信号,当rxf_n为低时,fpga可以通过驱动RD低来读取数据。input [7:0] data_in , //FT232h从上位机中读出的数据input wr_n , output reg rd_n , //output reg oe_n , //oe_n:驱动FT232H引脚上的数据输出到FPGA//fifo信号 input empty_o ,input full_o ,//input rst_busy ,output reg [7:0] data_wr , // data_wr_reg:要写入FPGA里面的FIFO的数据。output reg wr_fifo //fifo的写使能信号

);reg [7:0] data_wr_reg;reg rxf_n_r ;

reg wr_n_r ;

reg empty_o_r ;

reg oe_n_r;

reg rd_n_r;always@(posedge clk_60m or posedge reset)beginif(reset==1'b1)oe_n<=1'b1;else if(rxf_n==1'b0&&wr_n==1'b1) oe_n<=1'b0;else oe_n<=1'b1;

endalways@(posedge clk_60m or posedge reset)beginif(reset==1'b1)rd_n<=1'b1;else beginif(oe_n==0 && wr_n == 1&&rxf_n==1'b0) rd_n<=1'b0;elserd_n<=1'b1;end

endalways@(posedge clk_60m or posedge reset)beginif(reset==1'b1)rd_n_r<=1'b1;else beginrd_n_r<=rd_n;end

endalways@(posedge clk_60m or posedge reset)beginif(reset==1'b1)data_wr<='d0;else if(oe_n==1'b0&&wr_n==1'b1&&rd_n==1'b0)data_wr<=data_in;elsedata_wr<=8'h00;

end//wr_fifo:wr_fifo延迟rd_n一个周期

always@(posedge clk_60m or posedge reset)beginif(reset==1'b1)wr_fifo <= 1'b0;else if (rd_n_r==1'b1&&rd_n==1'b0&&rxf_n==1'b0&&full_o==1'b0&&wr_n==1'b1) wr_fifo <= 1'b1;else if(rxf_n==1'b1)wr_fifo <= 1'b0;elsewr_fifo<=wr_fifo;

endendmodule3.3 ft232h_recv

module ft232h_recv(input clk_60m ,input reset ,input txe_n ,input rd_n ,input oe_n ,input rxf_n ,input wr_fifo ,output reg wr_n ,output reg [7:0] data_out ,output reg [7:0] data_out_oe ,//fifo信号//input rst_busy ,input data_count ,input full_o ,input empty_o ,input [7:0] data_rd ,output reg rd_fifo ,output reg rd_fifo_flag_r,output reg rd_fifo_flag

);reg rd_fifo_r;

reg rd_fifo_flag;

//reg rd_fifo_flag_r;

reg empty_o_r ;always@(posedge clk_60m or posedge reset)beginif(reset==1'b1)empty_o_r<=1'b0;elseempty_o_r<=empty_o;

endalways@(posedge clk_60m or posedge reset)beginif(reset==1'b1)rd_fifo<=1'b0;else if(txe_n==1'b0&&empty_o==1'b0&&rd_n==1'b1)rd_fifo<=1'b1;elserd_fifo<=1'b0;

endalways@(posedge clk_60m or posedge reset)beginif(reset==1'b1)rd_fifo_flag<=1'b0;else if(rd_fifo==1'b1&&rd_fifo_r==1'b0)rd_fifo_flag<=1'b1;elserd_fifo_flag<=1'b0;

endalways@(posedge clk_60m or posedge reset)beginif(reset==1'b1)rd_fifo_flag_r<=1'b0;else rd_fifo_flag_r<=rd_fifo_flag;

endalways@(posedge clk_60m or posedge reset)beginif(reset==1'b1)rd_fifo_r<=1'b0;elserd_fifo_r<=rd_fifo;

endalways@(posedge clk_60m or posedge reset)beginif(reset==1'b1)begindata_out<='d0;endelsedata_out<=data_rd;

endalways@(posedge clk_60m or posedge reset)beginif(reset==1'b1)begindata_out_oe<='d0;endelse if(rd_fifo_flag==1'b1&&txe_n==1'b0&&empty_o==1'b0&&rd_n==1'b1)data_out_oe<=8'hff;else if(empty_o_r==1'b1||txe_n==1'b1)data_out_oe<='d0;elsedata_out_oe<=data_out_oe;

endalways@(posedge clk_60m or posedge reset)beginif(reset==1'b1)wr_n<=1'b1;else beginif(rd_fifo_flag==1'b1&&txe_n==1'b0&&empty_o==1'b0&&rd_n==1'b1)wr_n<=1'b0; else if(empty_o_r==1'b1||txe_n==1'b1)wr_n<=1'b1;elsewr_n<=wr_n;end

endendmodule

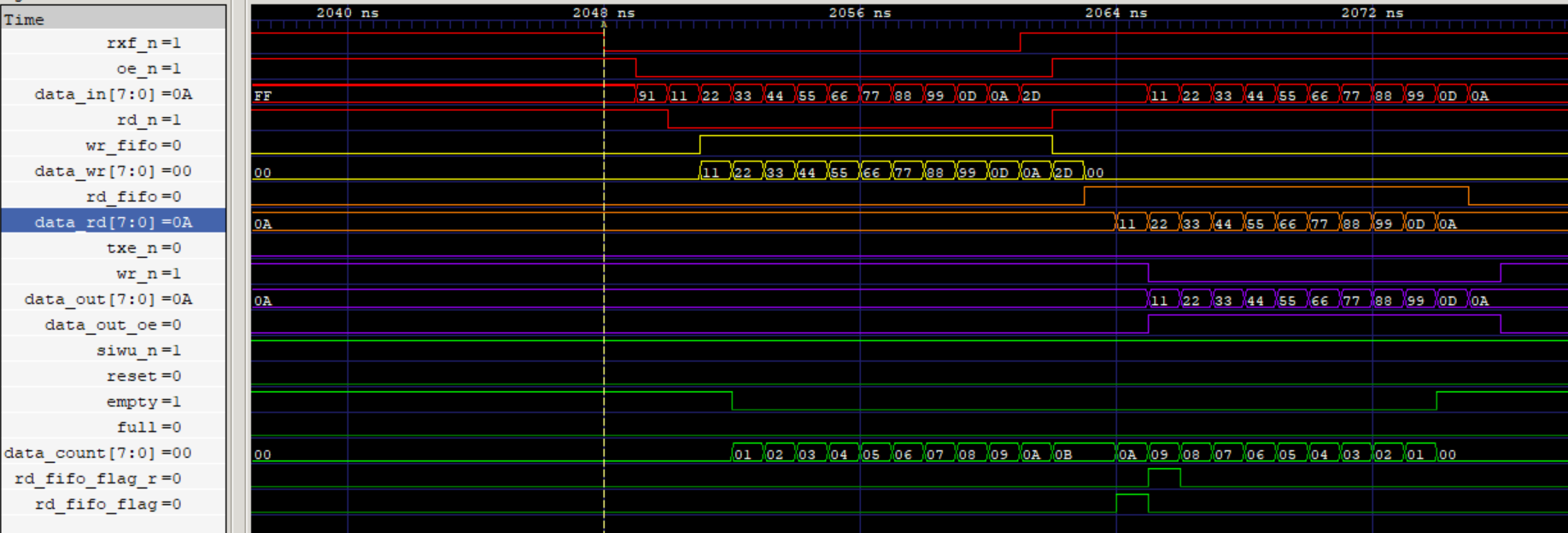

4.波形分析

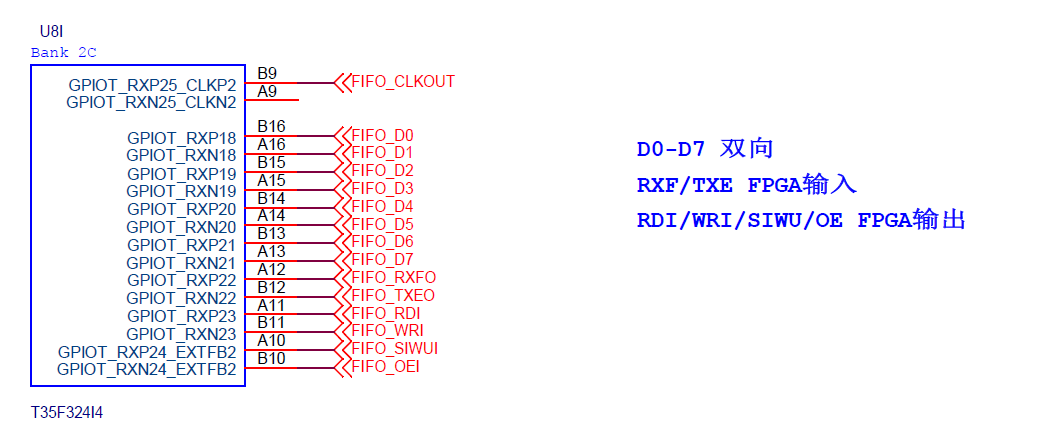

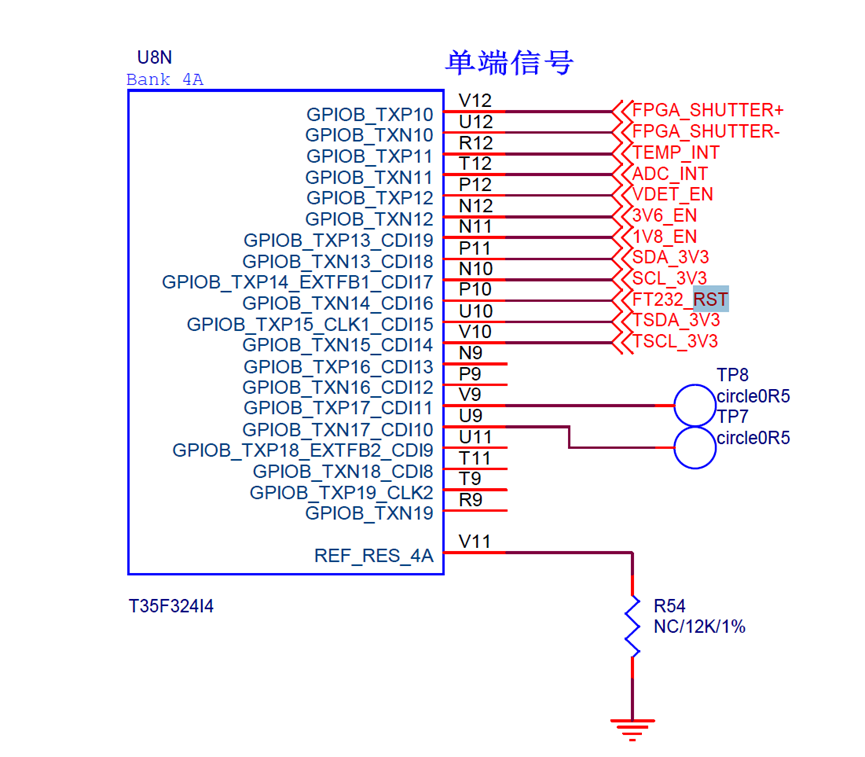

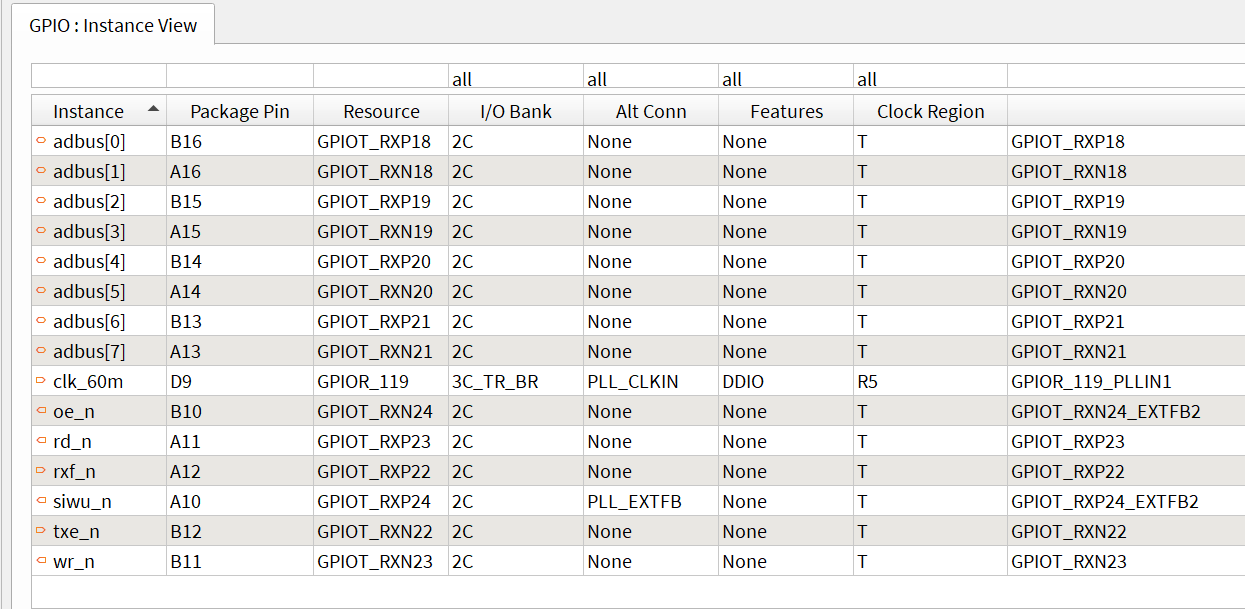

5.管脚绑定

6.注意事项

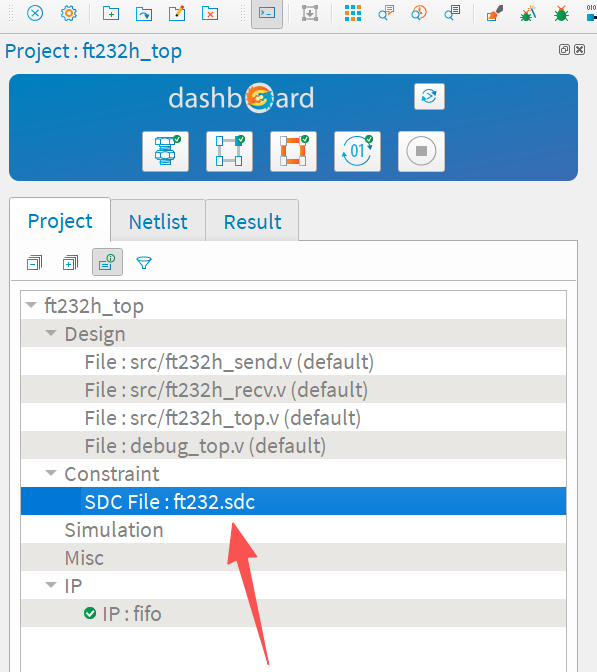

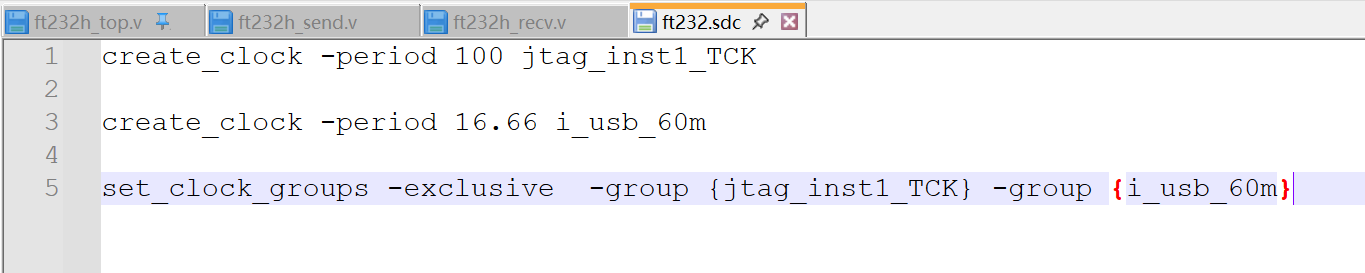

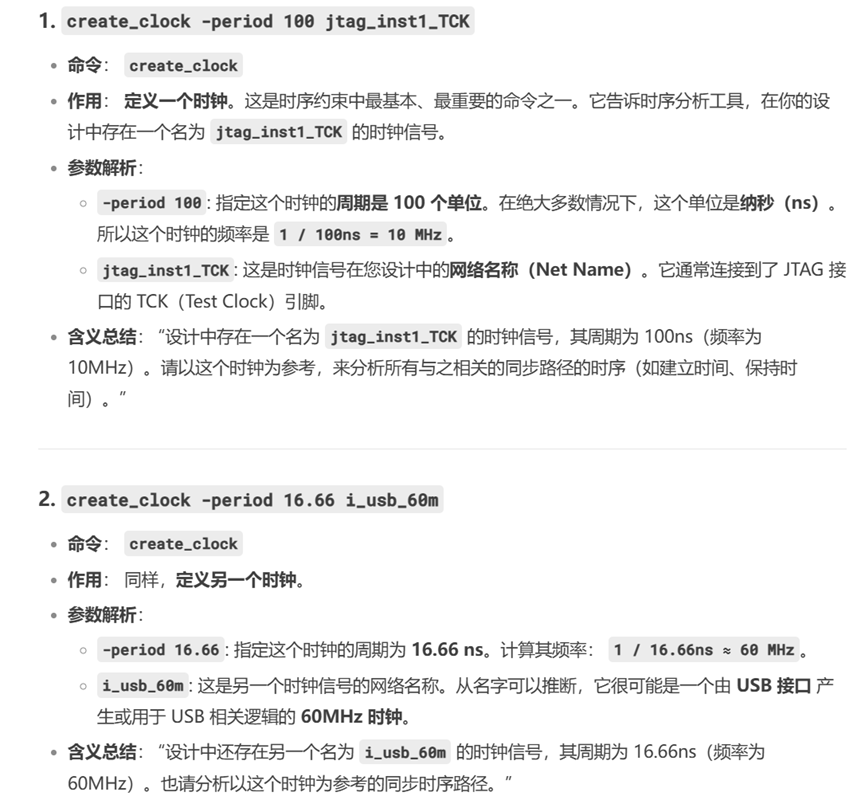

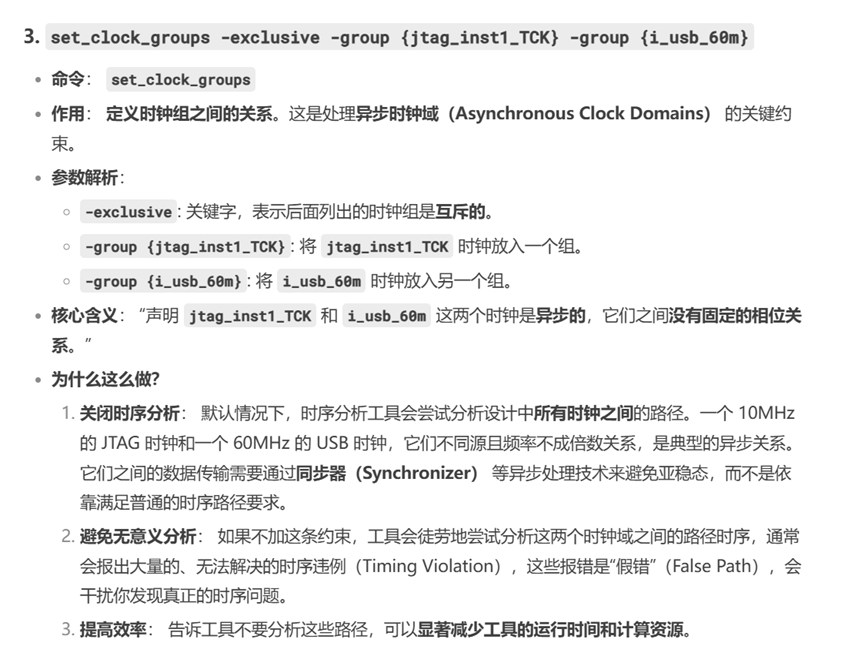

(1)如果要使用外部输入的时钟作为FPGA的工作时钟,需要对时钟进行约束。

例如:

(2)下载比特流文件出错的原因

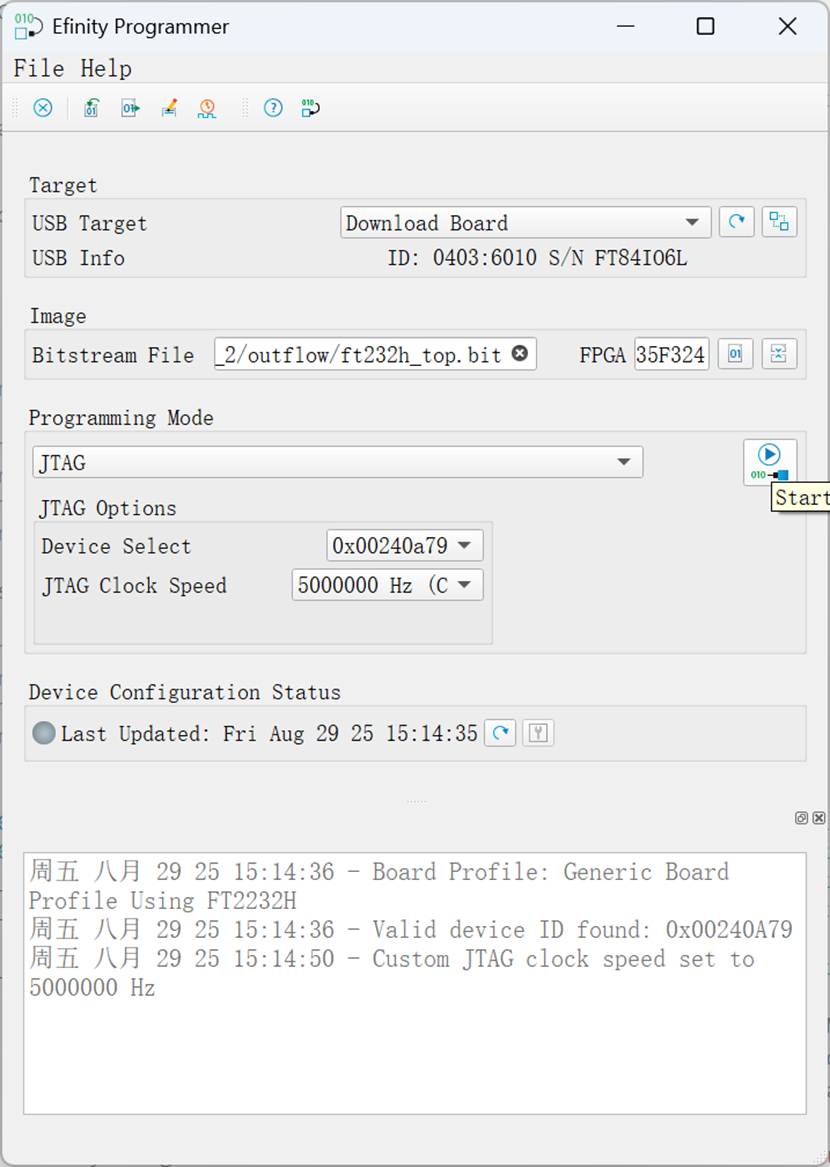

使用上面这个版本有bug,烧录比特流文件的时候,直接在下载比特流文件界面下载,把频率改成5mhz,然后再debug界面直接连接,不再下载。

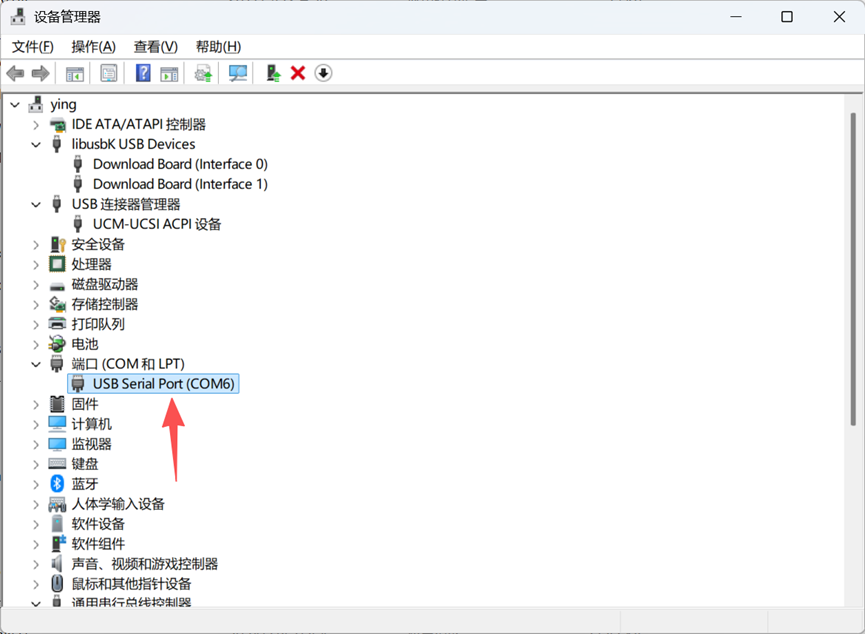

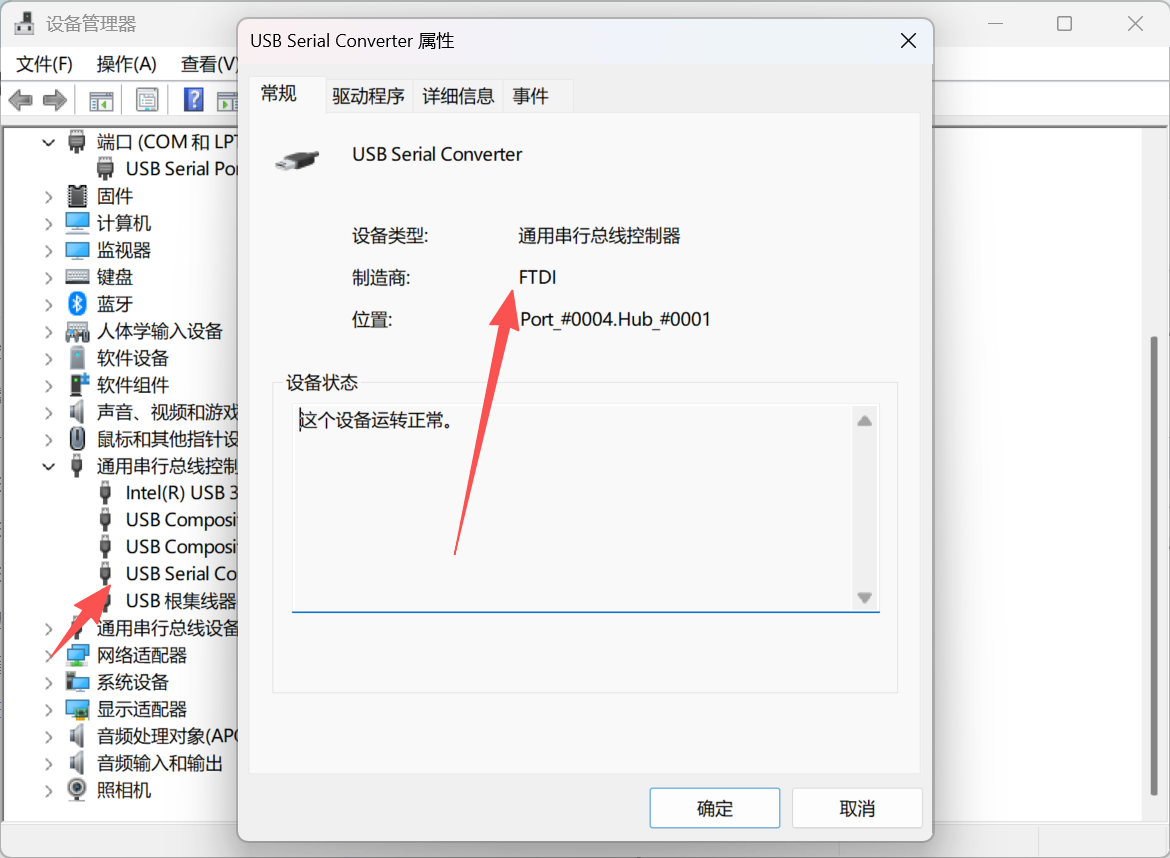

(3)连接usb线的时候需要下载正确的驱动

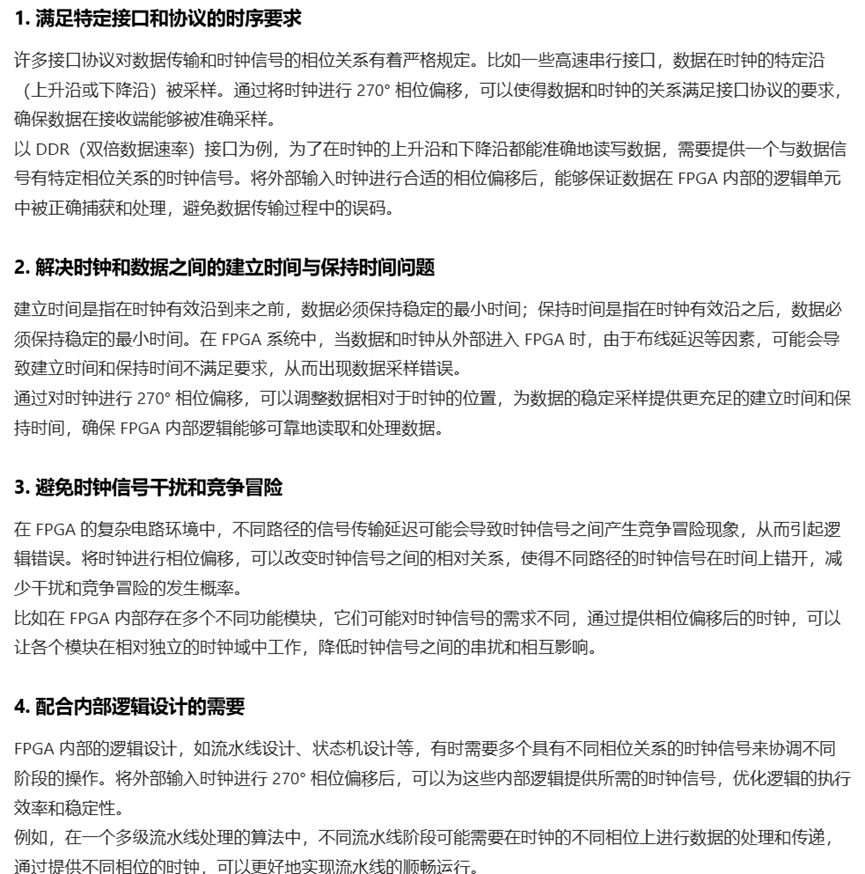

(4)为什么要用相位差为270°的时钟?

(5)PLL的使用说明

PLL用法

:在 Windows 上安装与配置 MATLAB(超详细))

)

)