大家好,欢迎来到我们的 DSP28335 深度解析系列。在之前的实战中,我们通过 while(1) 循环和延时函数实现了各种控制,这种方式被称为轮询。但轮询就像一个焦急的门卫,需要不停地去检查每个门口是否有人,既浪费精力又效率低下。今天,我们将学习一种更高效、更优雅的机制——中断 (Interrupt),为我们的系统装上“门铃”,让它从被动等待变为主动响应。

掌握中断系统,是从入门到精通的必经之路,是释放 DSP 真正潜能的关键。

一、中断是什么?—— 从“轮询”到“事件驱动”

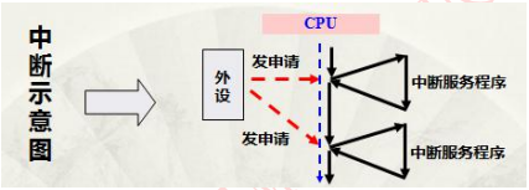

[图1: 中断示意图]

中断,顾名思义,就是打断当前正在执行的任务。在 CPU 执行程序时,如果发生了某个需要立即处理的紧急或随机事件(例如按键按下、定时器到时、数据接收完成),这个事件就会像一个“请求”,向 CPU 申请关注。CPU 在允许的情况下,会暂时挂起当前正在执行的程序,转而去执行一段专门为处理该事件而写的代码——即中断服务程序 (ISR, Interrupt Service Routine)。当事件处理完毕后,CPU 会自动返回到之前被打断的地方,继续执行原来的程序。

这一过程,就如同你在专心看书(主程序),突然电话铃响(中断请求),你于是放下书,拿起听筒接电话(执行ISR),讲完电话后,你再拿起书从刚才读到的地方继续看下去。

二、F28335 中断的宏观架构

TI 的 C2000 系列 DSP,尤其是 F28335,拥有一个非常强大且灵活的中断系统。

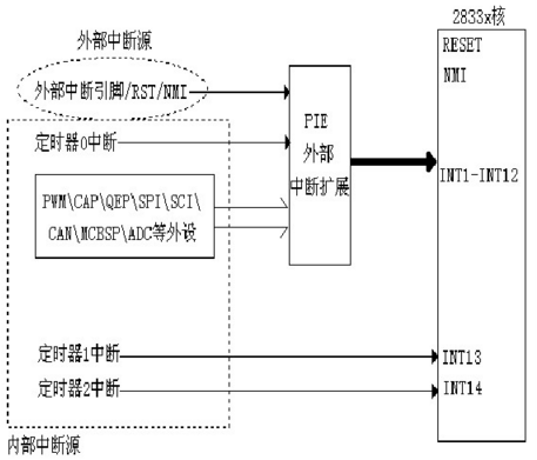

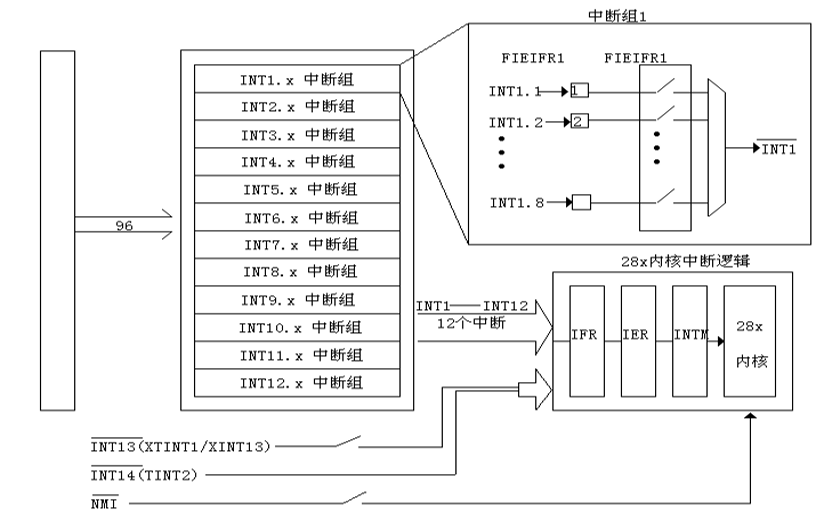

[图2: F28335 中断源与内核关系图]

16 条核心中断线: F28335 的 C28x 内核有 16 个中断入口。这包括 2 个不可屏蔽中断(RESET 和 NMI - Non-Maskable Interrupt,通常用于电源掉电等最高紧急事件),以及 14 个可屏蔽中断(INT1 ~ INT14)。

众多的中断源: 而 DSP 的外设远不止 14 个,ADC、ePWM、SPI、SCI、CAN、定时器等几十个模块都可能产生中断请求。

PIE 的诞生: 如何用 14 条中断线,管理几十个中断源?答案就是复用。PIE (Peripheral Interrupt Expansion) 模块应运而生,它像一个巨大的中断“集线器”或“管理器”,负责将众多的外设中断请求,分门别类地汇总到 CPU 的 12 条主中断线(INT1 ~ INT12)上。

三、三级中断机制:从申请到批准的层层关卡

F28335 的中断响应过程像一个严格的“三级审批”流程。一个外设的中断请求,必须依次通过外设级、PIE 级和 CPU 级三道“门禁”,才能最终得到 CPU 的响应。

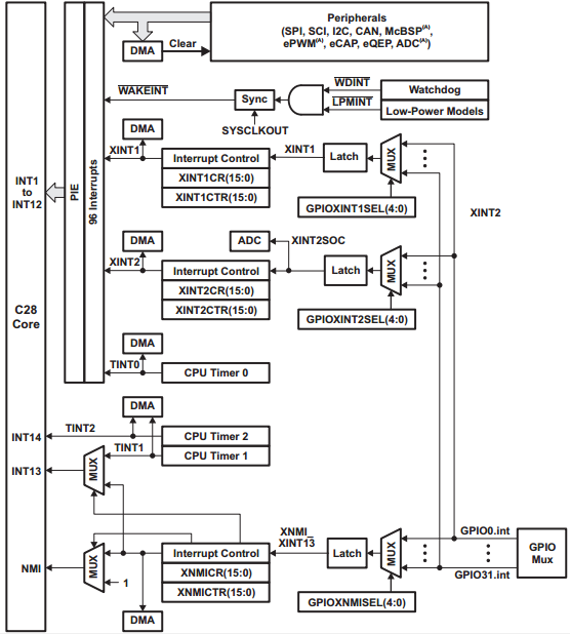

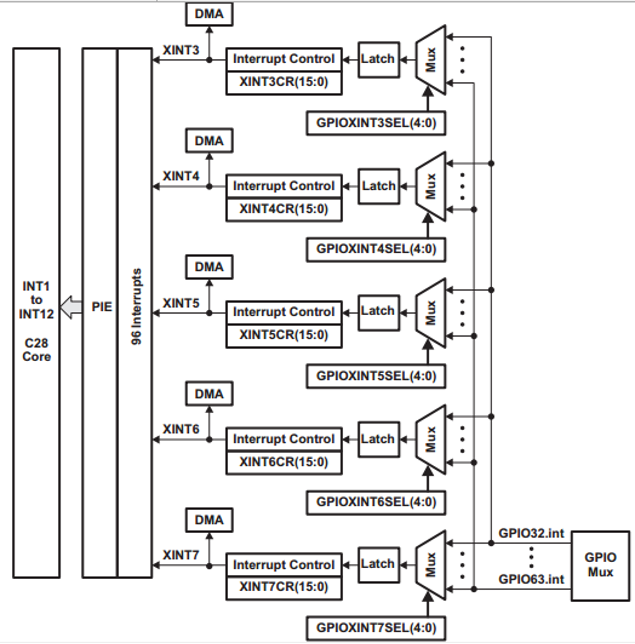

[图3 & 图4: 外部中断信号通路图]

第一级:外设级中断使能

关卡描述: 这是中断请求的源头。每个能够产生中断的外设模块(如 ADC、ePWM),其内部都有自己的中断使能位。

放行条件: 必须将对应外设的中断使能位置 1,它才被“允许”发出中断请求。如果这里是关闭的,那它连“喊一声”的机会都没有。

第二级:PIE 级中断使能

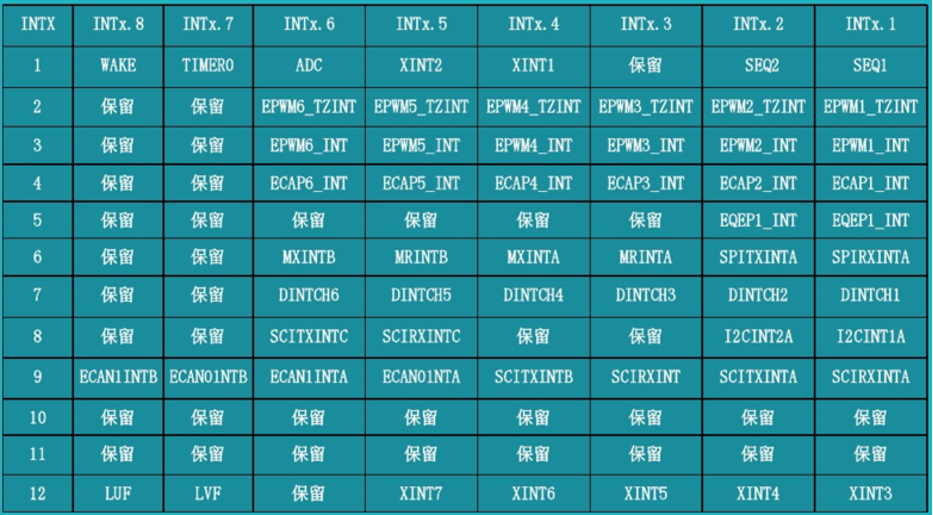

关卡描述: 这是中断请求的分组管理中心。PIE 模块将 96 个中断源分成了 12 个大组(PIE Group 1 ~ 12),每个大组包含 8 个中断。

[图6: PIE 96路中断分组逻辑图]

放行条件: 中断请求到达 PIE 后,需要通过两个“开关”:

PIEIFRx.y (中断标志位): 当中断请求到达,对应的标志位会自动置 1,表示“有人敲门了”。

PIEIERx.y (中断使能位): 必须将这个使能位置 1,表示“允许这扇门打开”。这个 x 代表组号 (1-12),y 代表组内中断号 (1-8)。

核心工作: 只有当 PIEIFR 和 PIEIER 中对应的位都为 1 时,该中断请求才能通过 PIE 这一级,并被提交给 CPU 对应的主中断线(例如,第3组的所有中断请求,最终都会汇集到 CPU 的 INT3 中断线上)。

[图7: PIE 中断向量表]

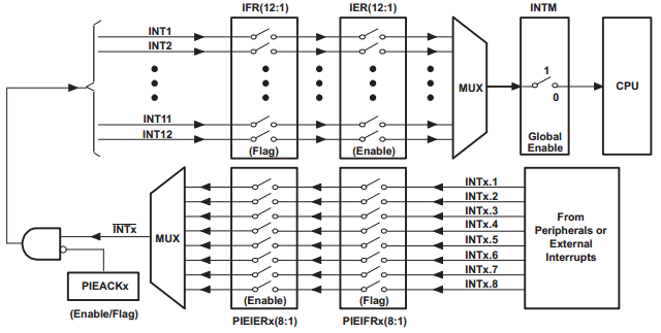

第三级:CPU 级中断使能

关卡描述: 这是中断请求的“总开关”和“最后一道防线”,直接与 CPU 内核相连。

[图5: PIE 与 CPU 中断逻辑细节图]

放行条件: PIE 提交的中断请求到达 CPU 后,同样需要通过两个“开关”:

IFR (中断标志寄存器): 当 INTx (x=1~14) 上有中断请求时,IFR 对应的位会置 1。

IER (中断使能寄存器): 这是 14 个主中断线的使能开关。必须用 IER |= M_INTx 的方式,打开对应中断线的“阀门”。

INTM (全局中断使能位): 这是全局的总开关。只有当 INTM 为 0 时,CPU 才响应中断。我们可以用汇编指令 EINT (Enable INTerrupt) 来清零它,或用 DINT (Disable INTerrupt) 来置位它。

总结:一个中断要想最终被 CPU 响应,必须同时满足:①外设中断使能打开 ②PIE 组中断使能打开 ③CPU 主中断线使能打开 ④CPU 全局中断使能打开。

四、中断响应:找到正确的服务程序 (中断向量表)

当中断请求历经千辛万苦终于获得批准后,CPU 需要知道应该去哪里执行对应的中断服务程序(ISR)。存放这些 ISR 入口地址的表,就叫做中断向量表 (Interrupt Vector Table)。

中断向量: 每个 ISR 的入口地址就是一个中断向量。它是一个 22 位的地址。

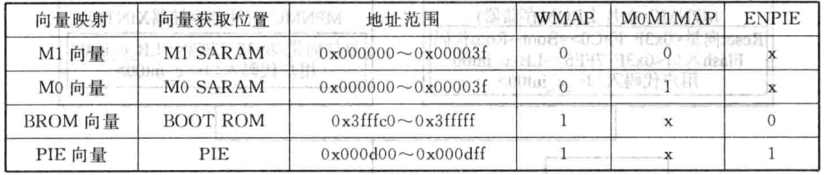

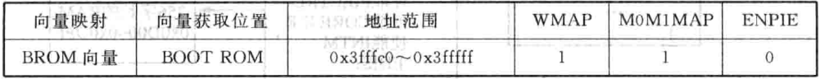

中断向量表: F28335 中,这个向量表可以被映射到不同的物理存储区域,这由三个关键的控制位来决定。

ENPIE (在 PIECTRL 寄存器中): PIE 模块的总开关。当它为 1 时,PIE 功能开启。复位后为 0。

VMAP (在 ST1 状态寄存器中): 控制向量是映射到内存低地址区还是高地址区(BOOT ROM)。复位后为 1。

M0M1MAP (在 ST1 状态寄存器中): 用于区分 M0 和 M1 RAM。复位后为 1。

实际应用中的选择:

[图8: PIE 使能时的向量映射表]

[图9: PIE 禁用时的向量映射表]通过查阅这两张表格,我们可以得出在实际应用中最常用的配置:

我们将 ENPIE 置 1,同时保持 VMAP=1 和 M0M1MAP=1。

在这种配置下,中断向量表被稳稳地映射到了 F28335 的 PIE RAM 区 (0x000D00 - 0x000DFF)。这样做的好处是,我们可以非常方便地在程序中,将我们自己编写的 ISR 函数的地址,注册到这个 RAM 区域的向量表中,从而将中断源和我们的服务程序动态地“链接”起来。

总结

DSP28335 的中断系统初看复杂,但其设计逻辑清晰、层次分明:

架构上,通过 PIE 模块实现了对海量中断源的分级管理。

响应上,通过“外设-PIE-CPU”的三级审批流程,确保了中断响应的严谨性和可控性。

寻址上,通过灵活的向量表映射机制,让用户可以方便地自定义中断服务程序。

虽然理论略显枯燥,但彻底理解这一套机制,是你编写高效、稳定、强大的嵌入式程序的基石。在下一篇章中,我们将进入实战,亲手配置一个定时器中断,让你真正感受到中断带来的编程魅力。

文本预处理:NLP 版 “给数据洗澡” 指南)

![[系统架构设计师]系统架构基础知识(一)](http://pic.xiahunao.cn/[系统架构设计师]系统架构基础知识(一))