总 :STM32——学习总纲

参考资料:

STM32F1系列参考手册-V10(中)

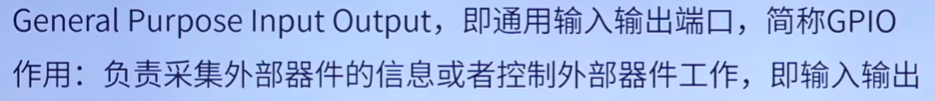

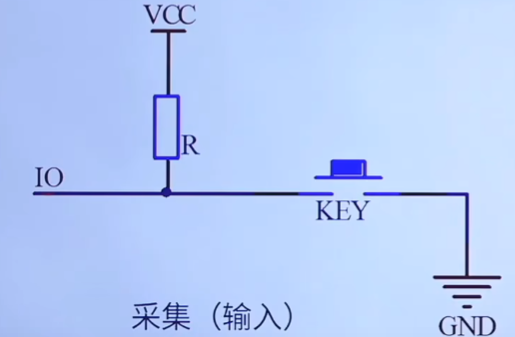

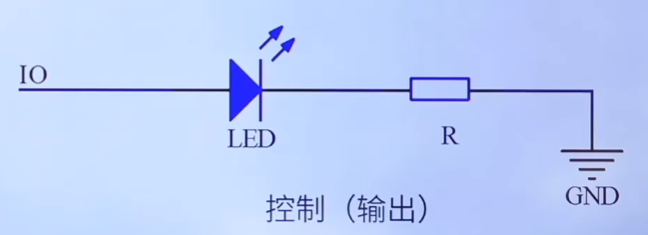

一、GPIO简介

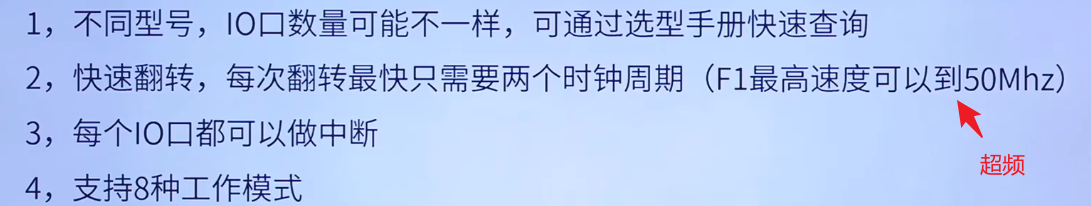

1.1 GPIO 特点

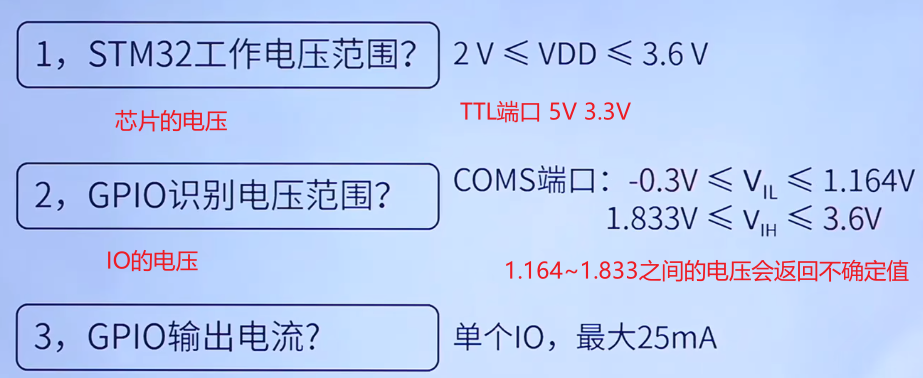

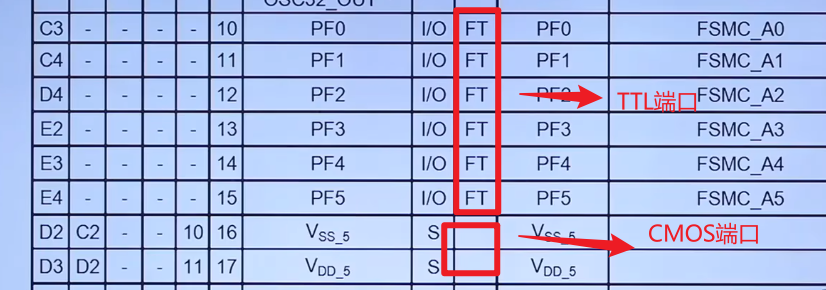

1.2 GPIO 电气特性*

stm32芯片资料STM32F103ZET6(English)

![]()

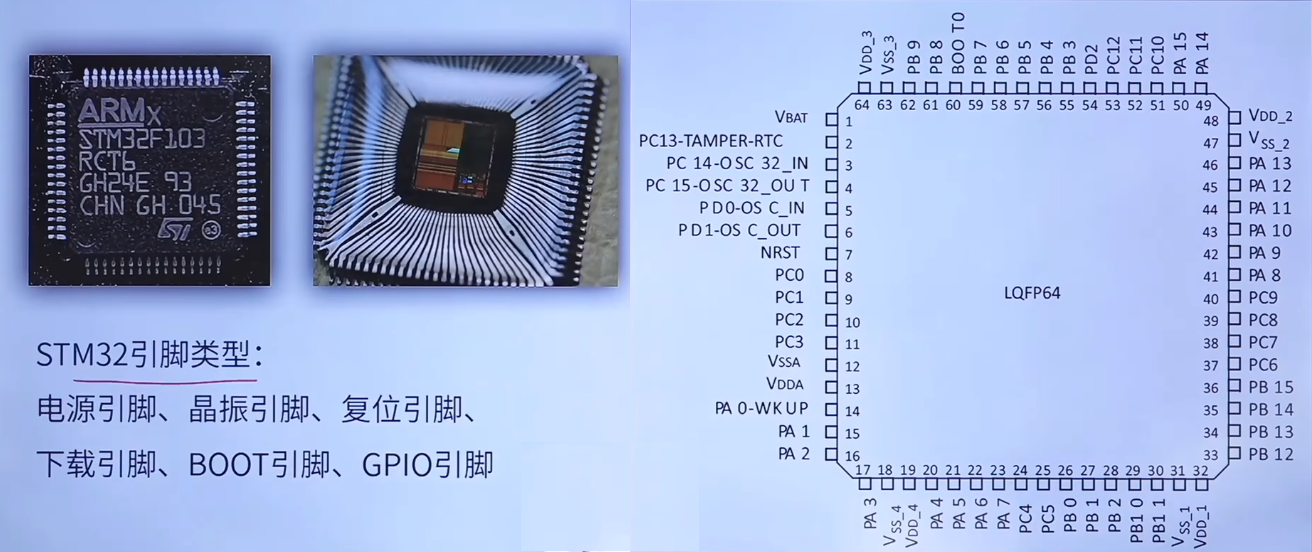

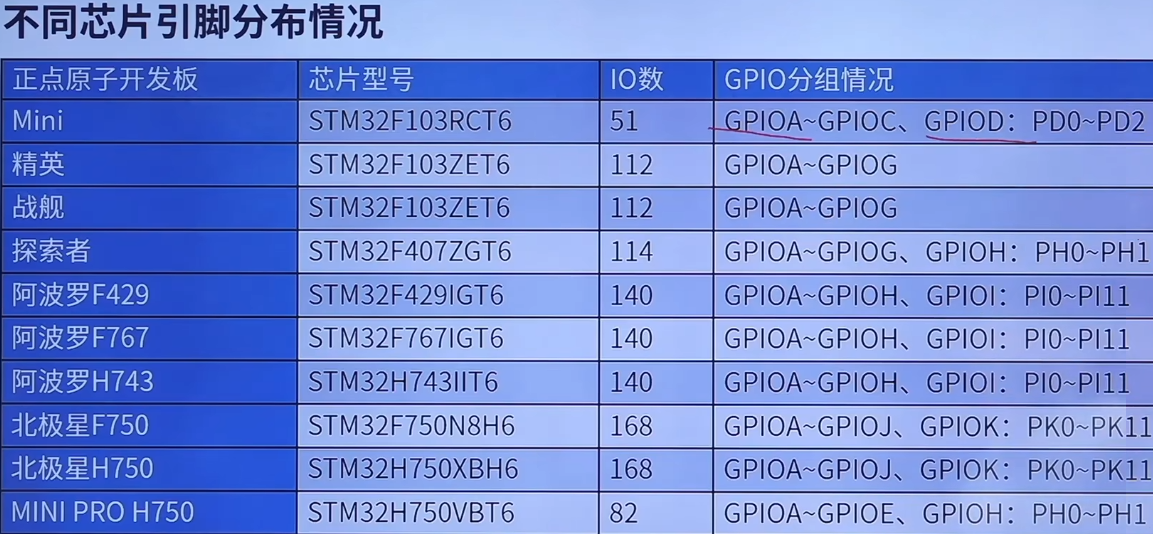

1.3 GPIO 引脚分布

电源引脚:V开头![]()

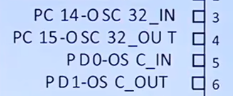

晶振引脚:

复位引脚:![]()

下载引脚:通过 串口、JTAG、SWD下载有不同的下载IO

BOOT引脚:

GPIO引脚:p开口

![]()

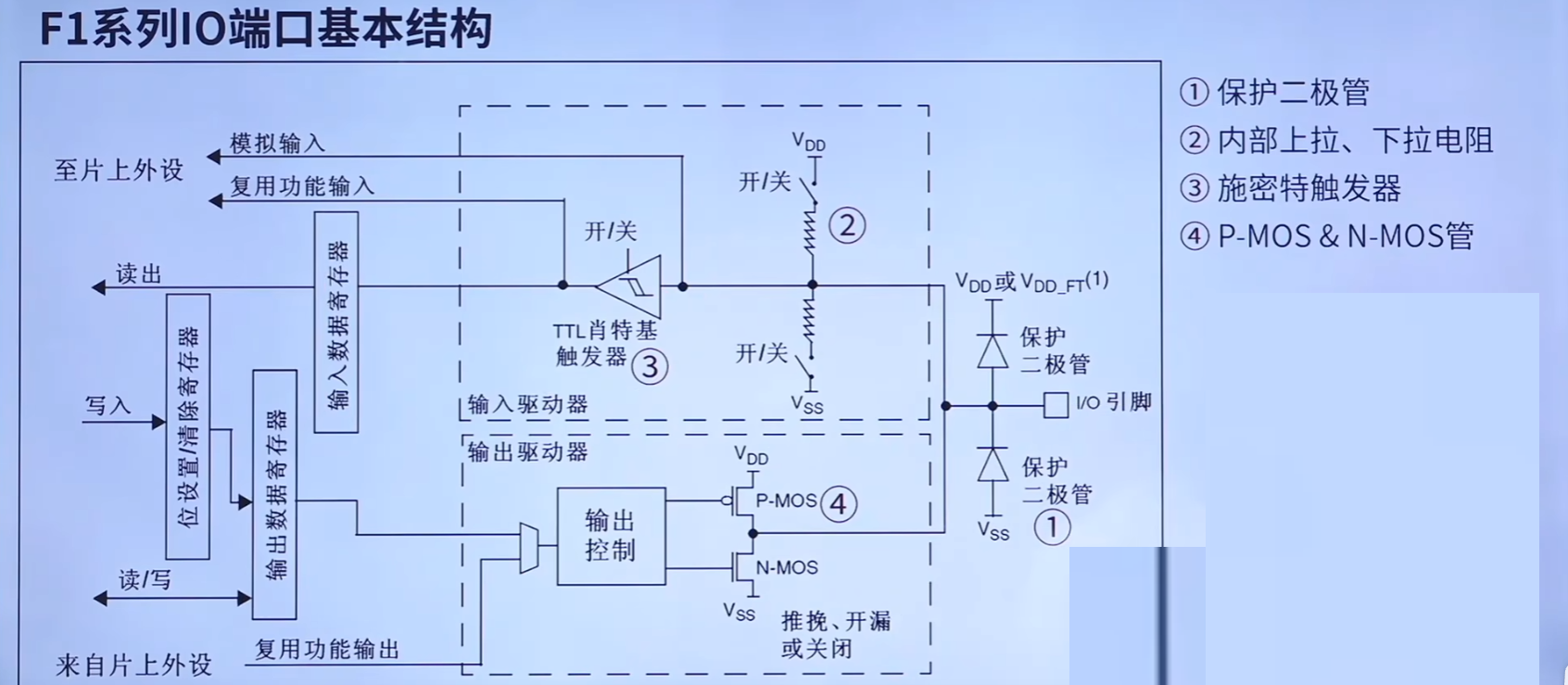

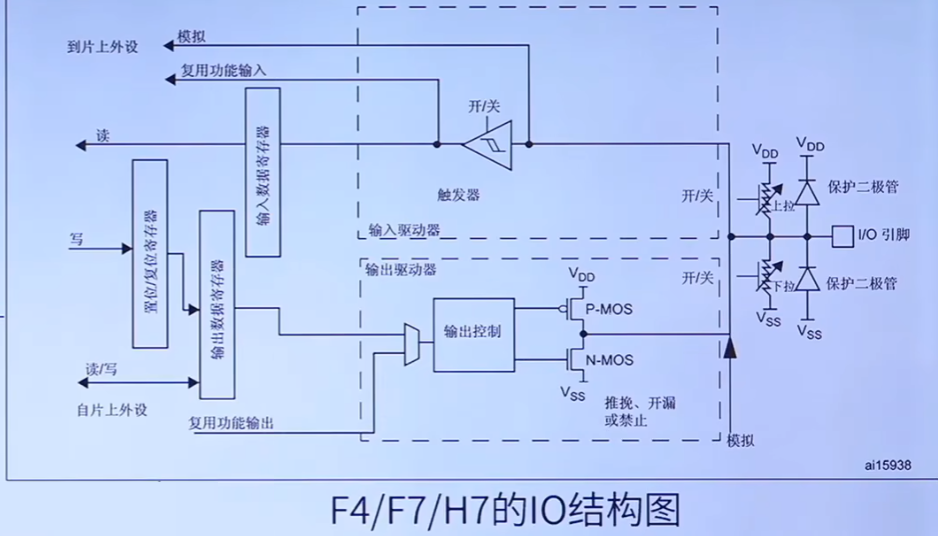

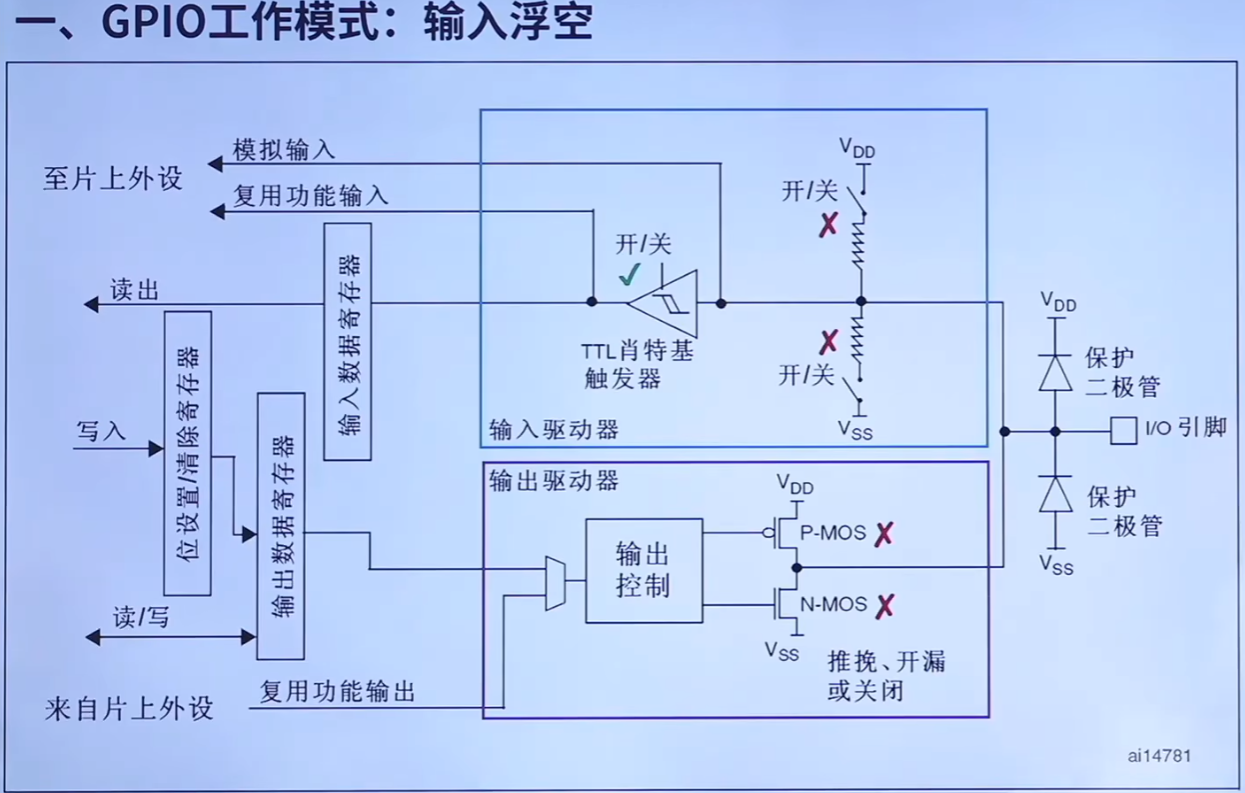

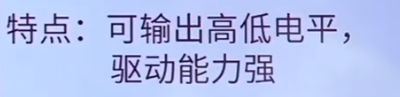

二、IO端口基本结构

F1与F3、F7、H7的差异点在于上下拉电阻的位置。

F1的IO做为输入禁止使用上下拉电阻,这是由硬件决定的。

额外补充:

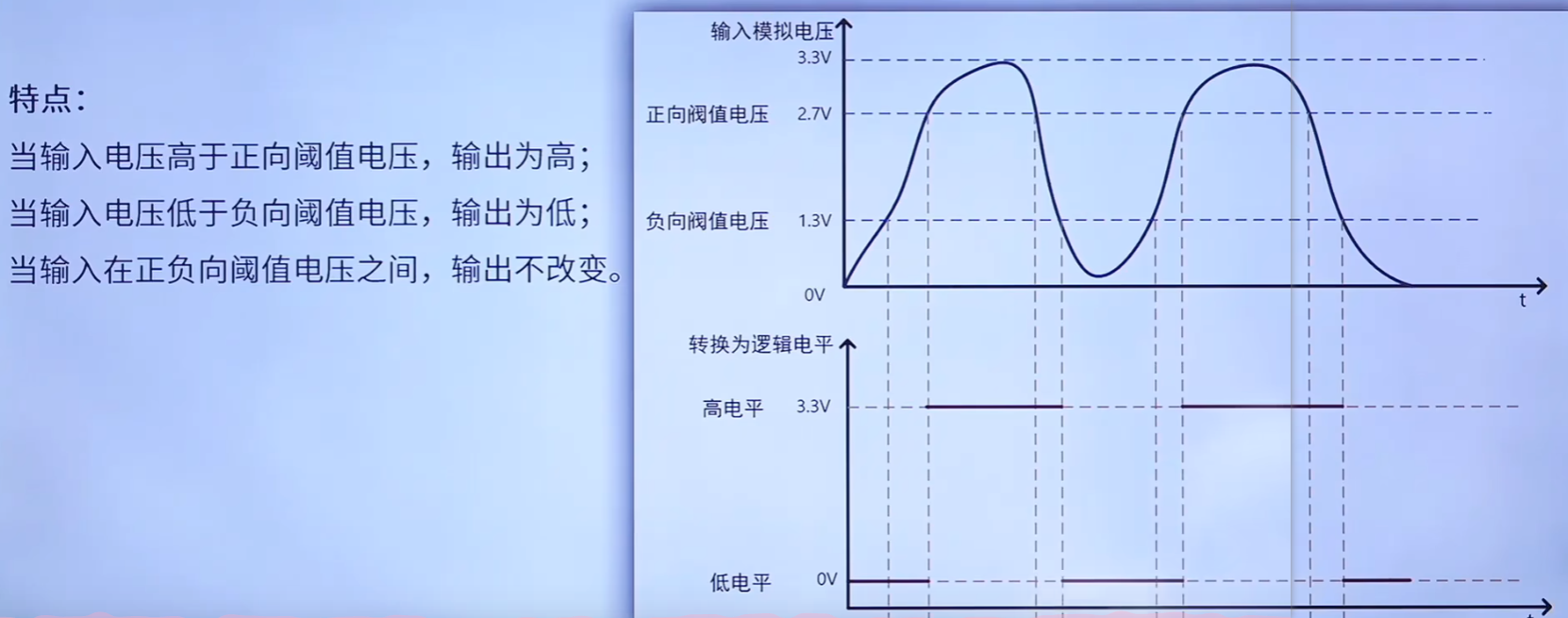

模电学习——场效应管(FET)

记忆:箭头方向就是电子流动方向。想要mos管导通,需要 gs 压差满足 箭头方向上的电子流通。

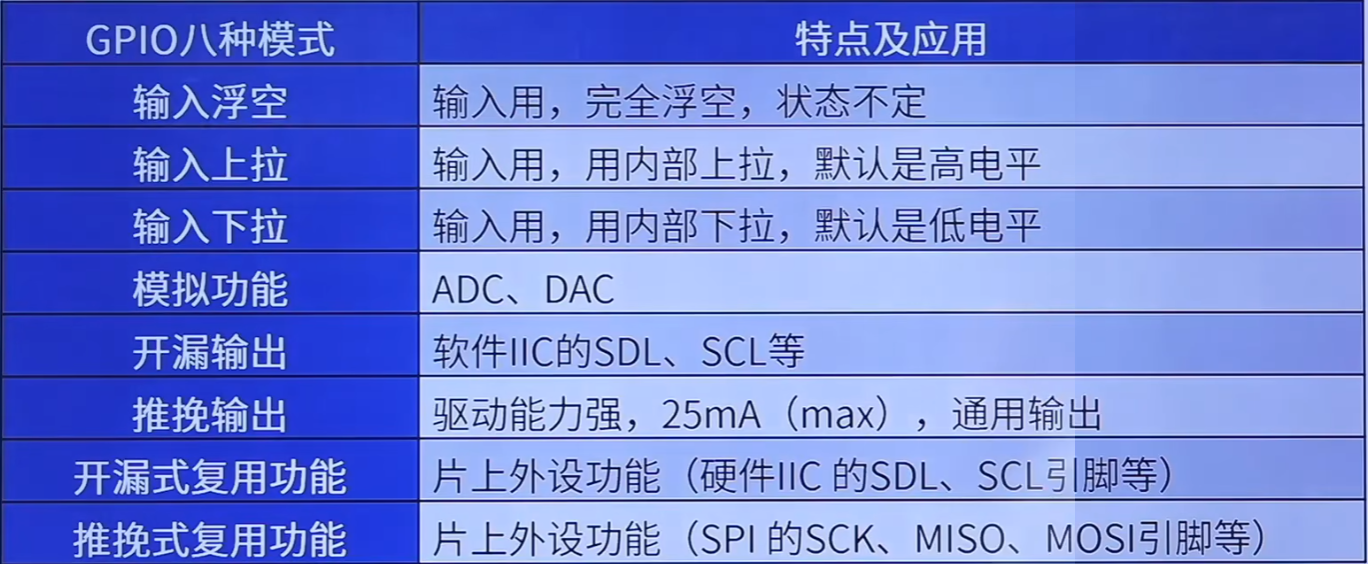

三、GPIO的八种模式(F1)

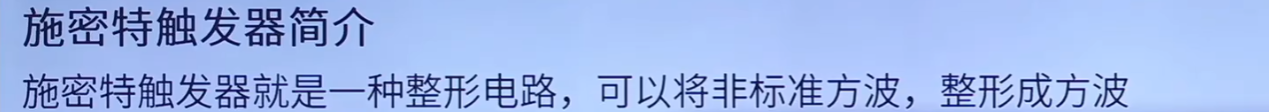

前置

STM32F1系列参考手册-V10(中)

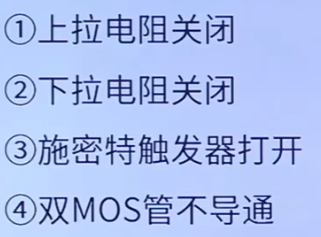

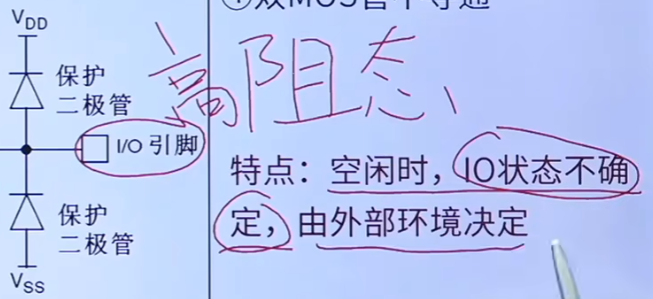

3.1 输入浮空

特点:

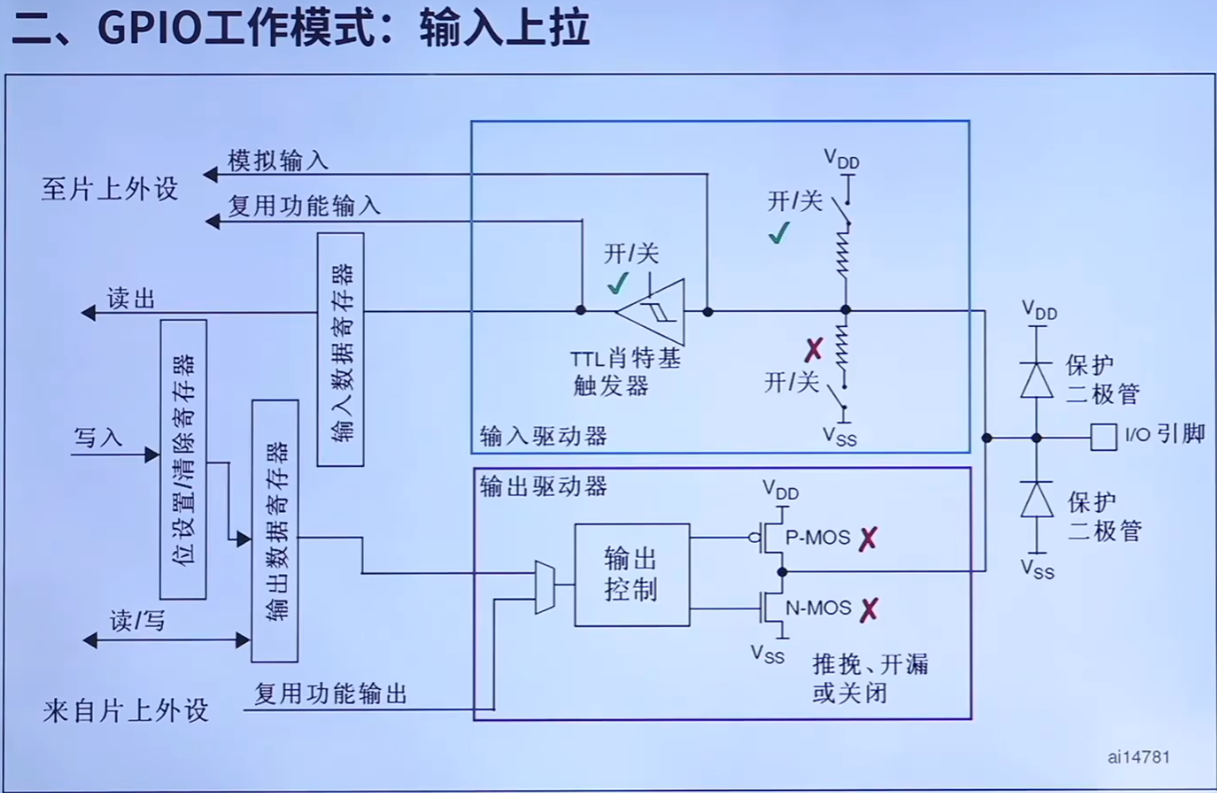

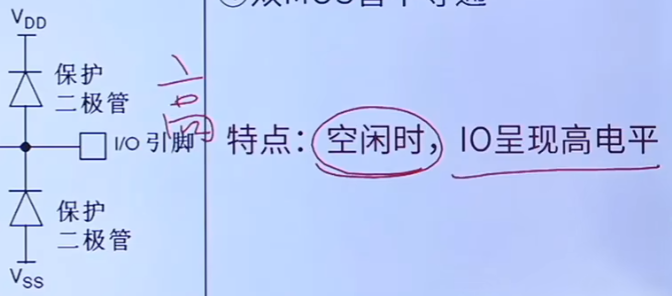

3.2 输入上拉

特点:

弱上拉

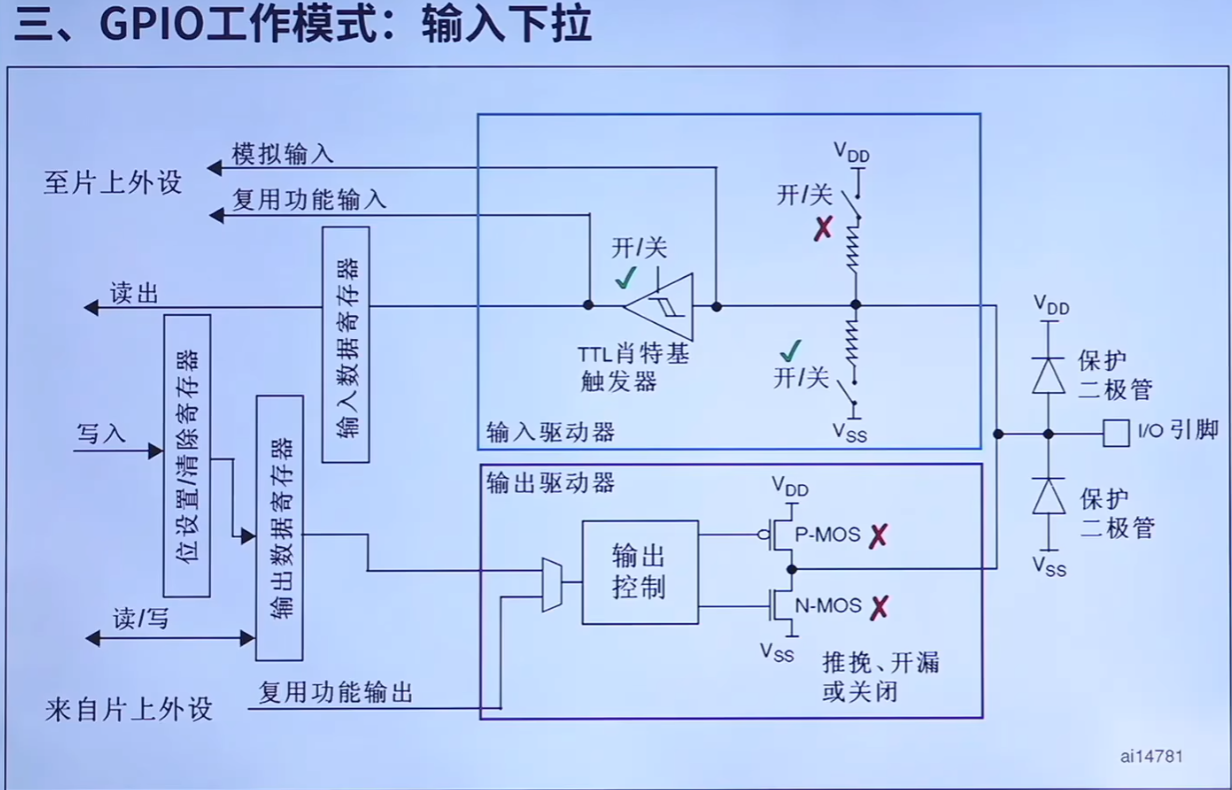

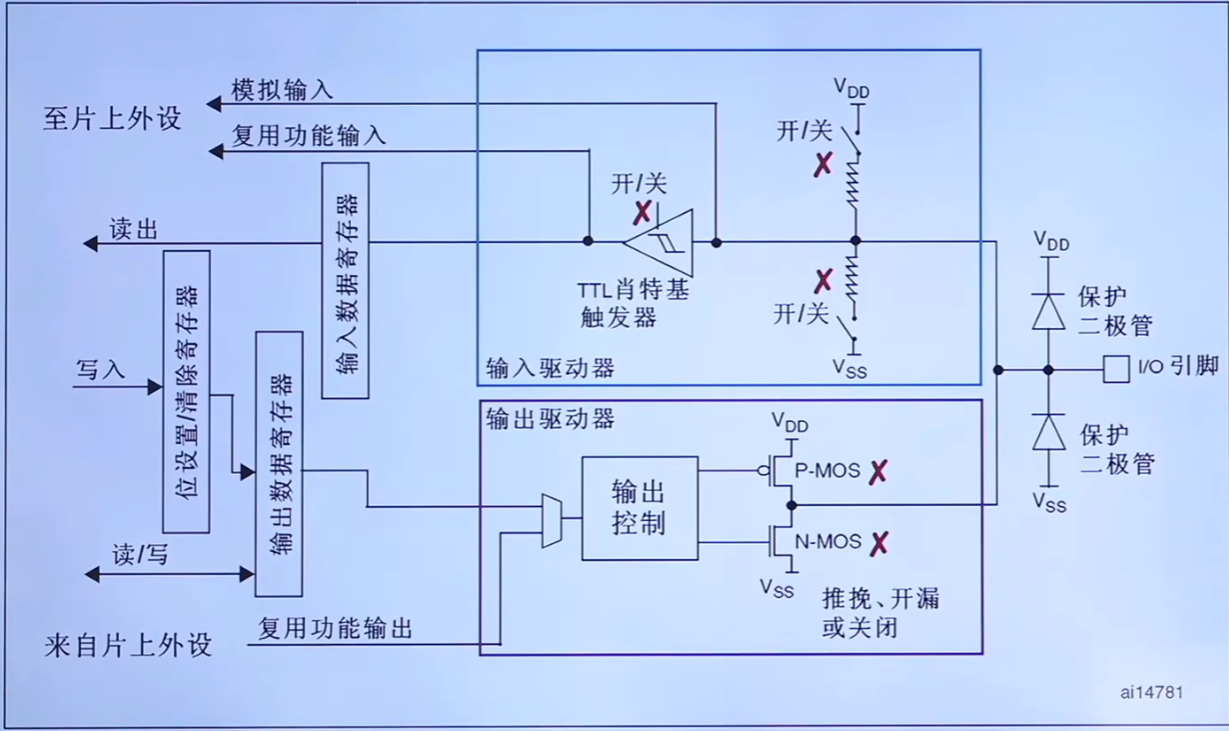

3.3 输入下拉

特点:

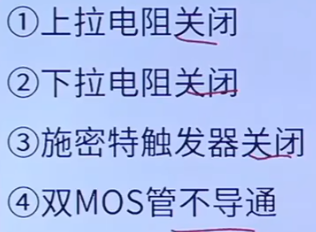

3.4 模拟功能

特点:

输入只走模拟输入

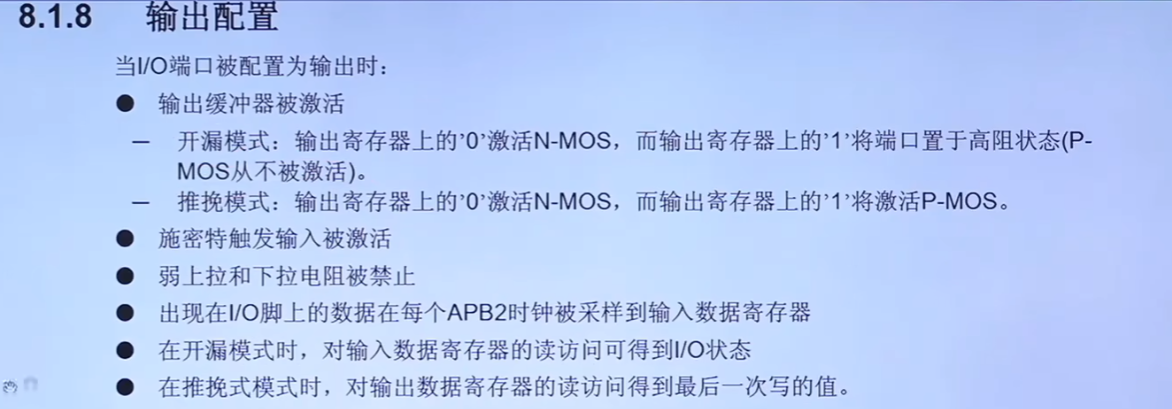

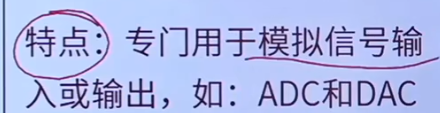

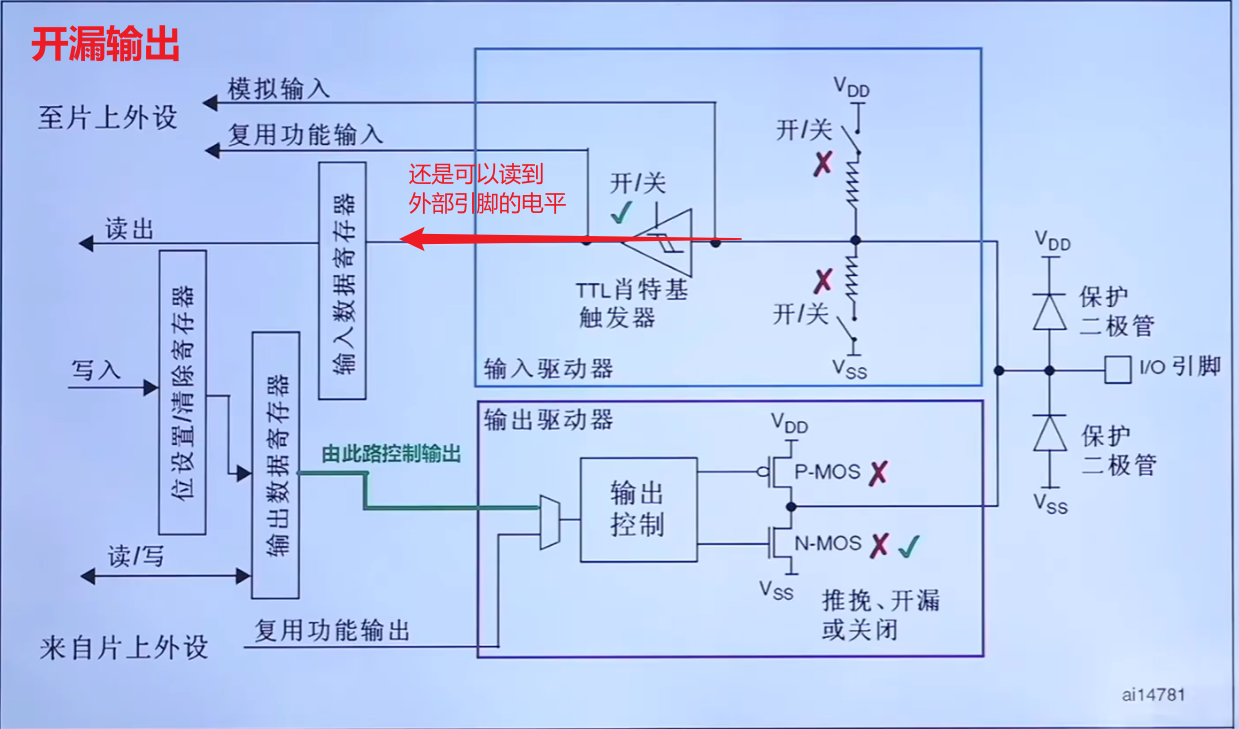

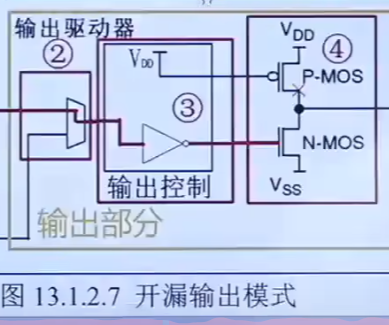

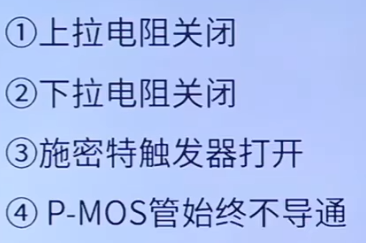

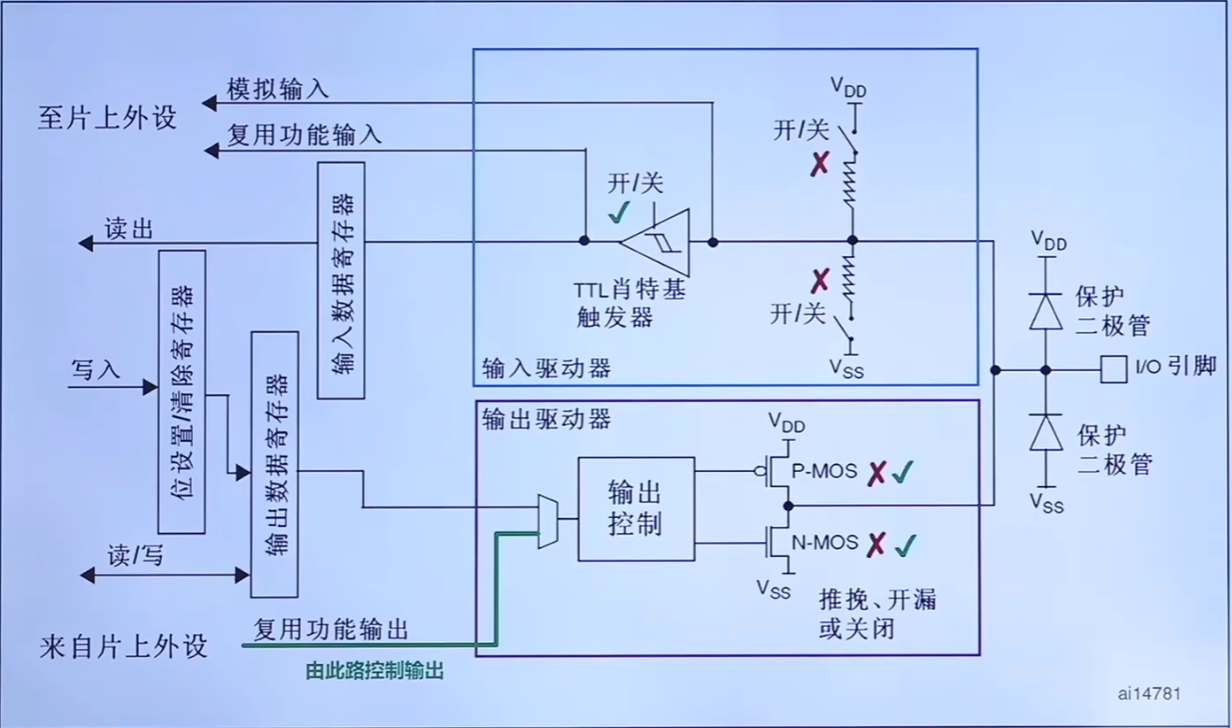

3.5 开漏输出

寄存器介绍参考前置

特点:

开漏模式下,寄存器写0,NMOS管导通,此时IO口呈低电平↓

开漏模式下,寄存器写1,P、N mos管皆不导通,此时IO口为高阻态,F1系列想要输出高电平,需要外部的上拉电阻。

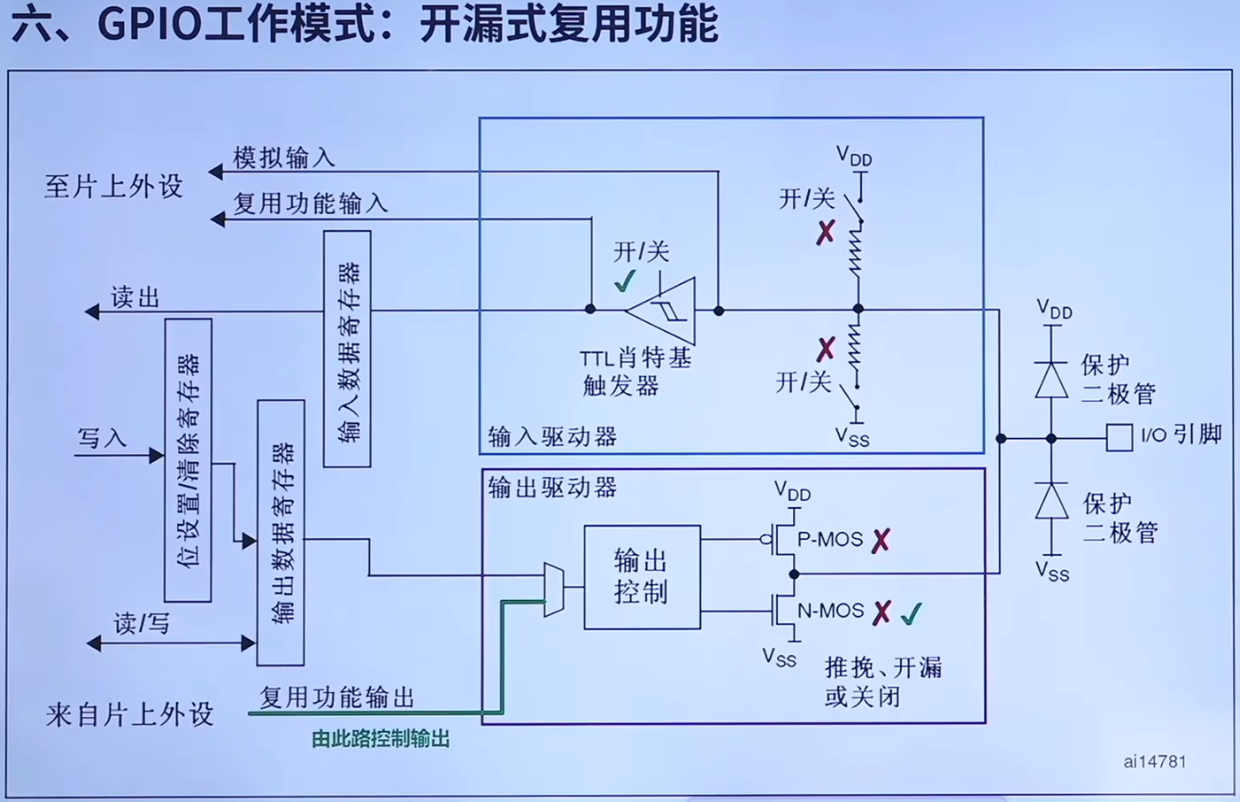

3.6 开漏复用

特点:

不由寄存器控制,由片上外设控制输出

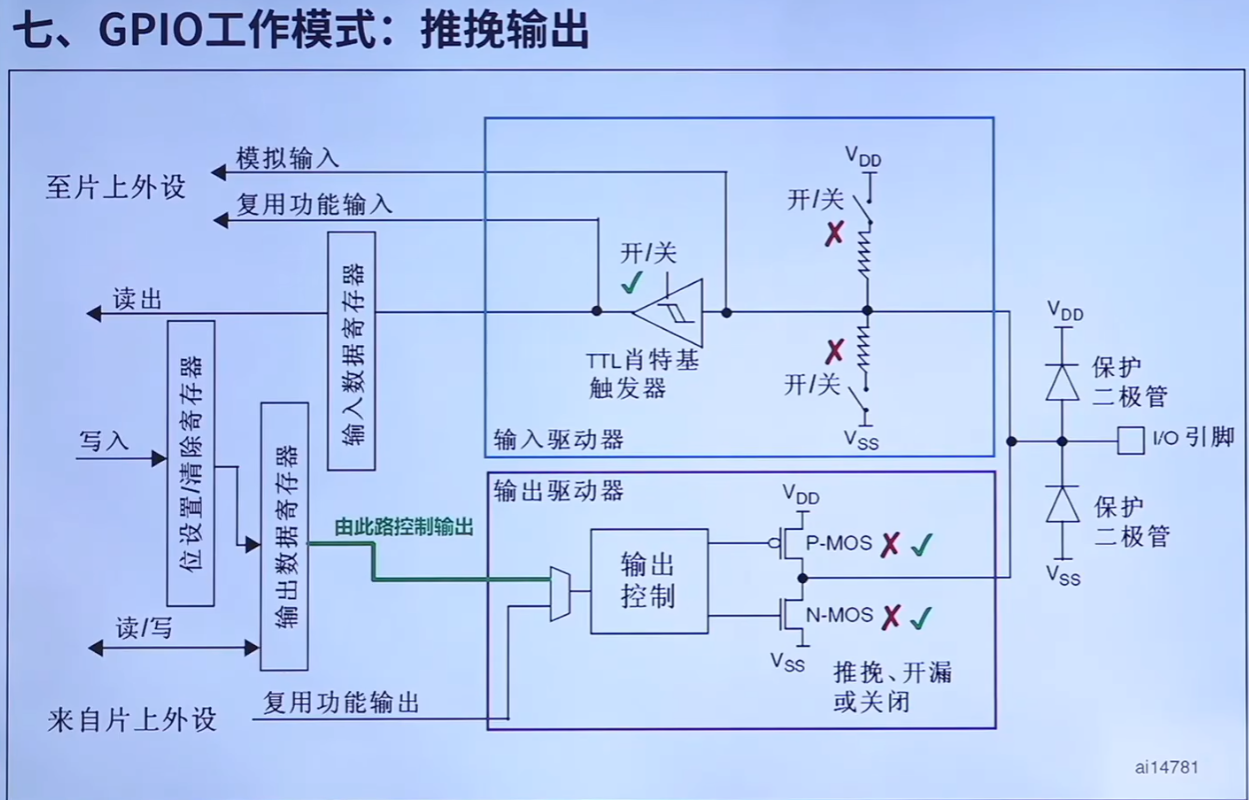

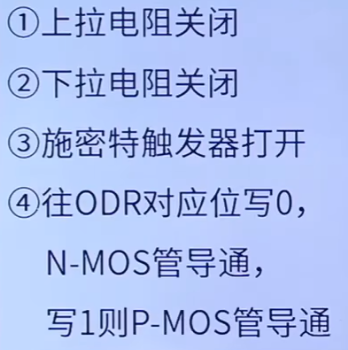

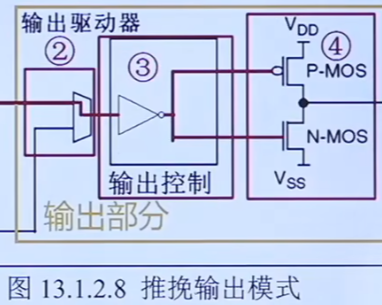

3.7 推挽输出

寄存器介绍参考前置

特点:

可控制 P/N MOS管的反向导通,控制 IO 口输出高低电平。

3.8 推挽复用

特点:

不由寄存器控制,由片上外设控制输出

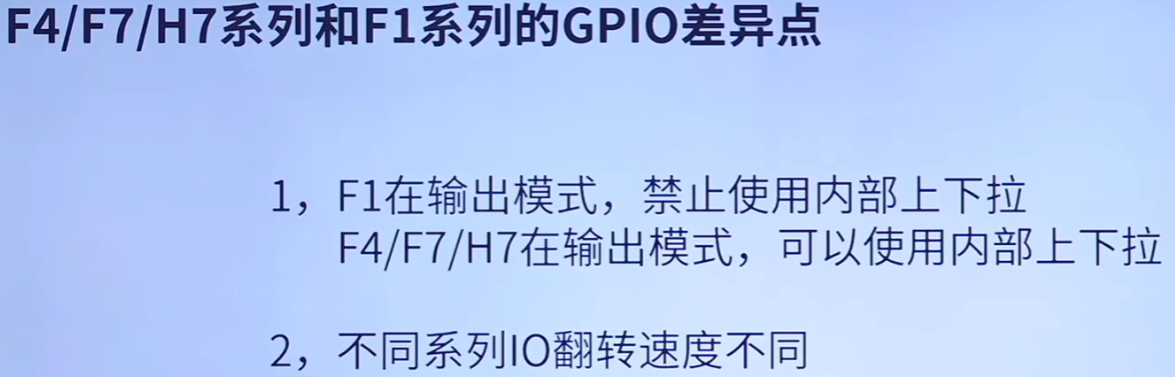

3.* F4/F7/H7 系列和 F1 系列的 GPIO 差异点

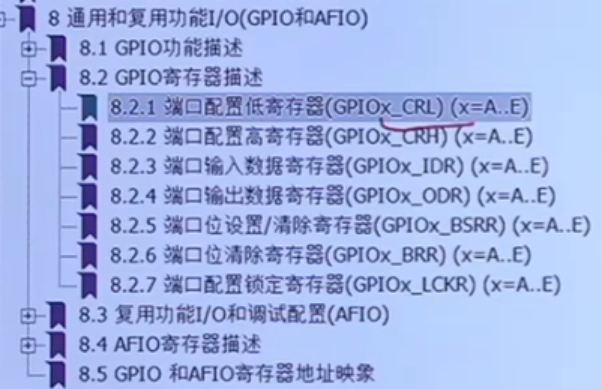

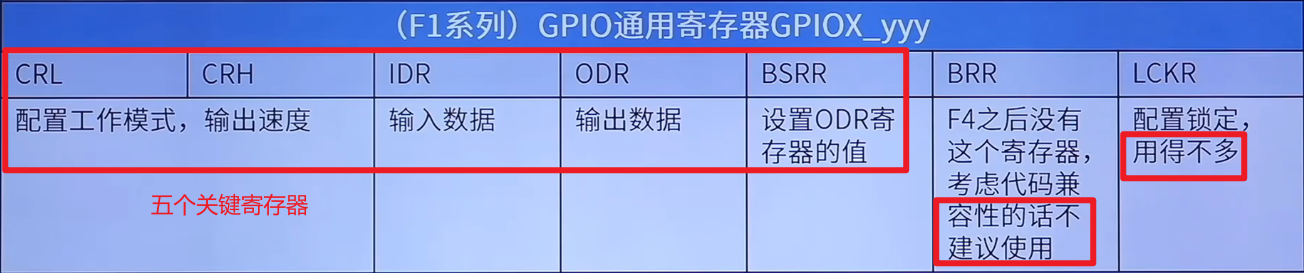

四、GPIO寄存器(F1)

STM32F1系列参考手册-V10(中)

“GPIOx_” 中的 ‘x’ 代表A~E组别,每个组有以下七个寄存器

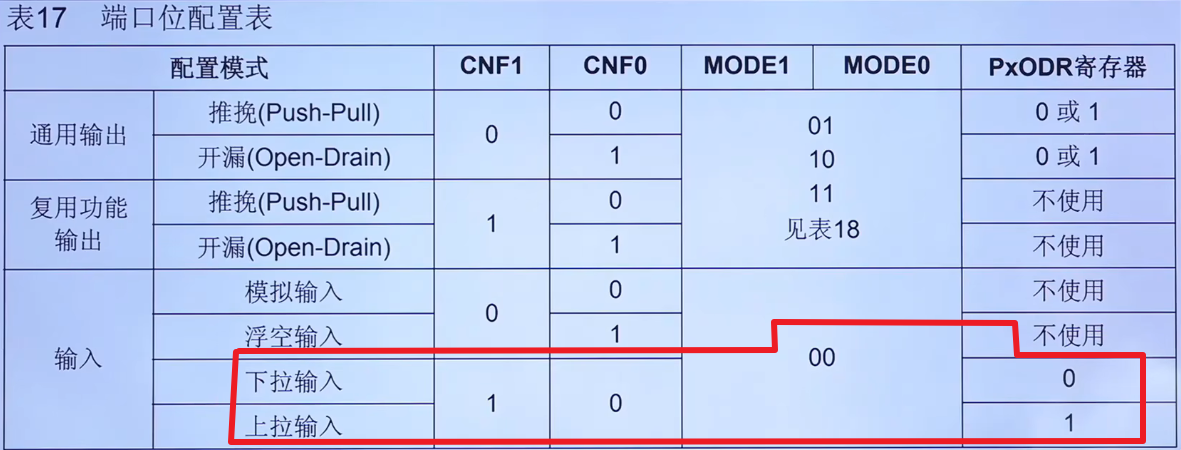

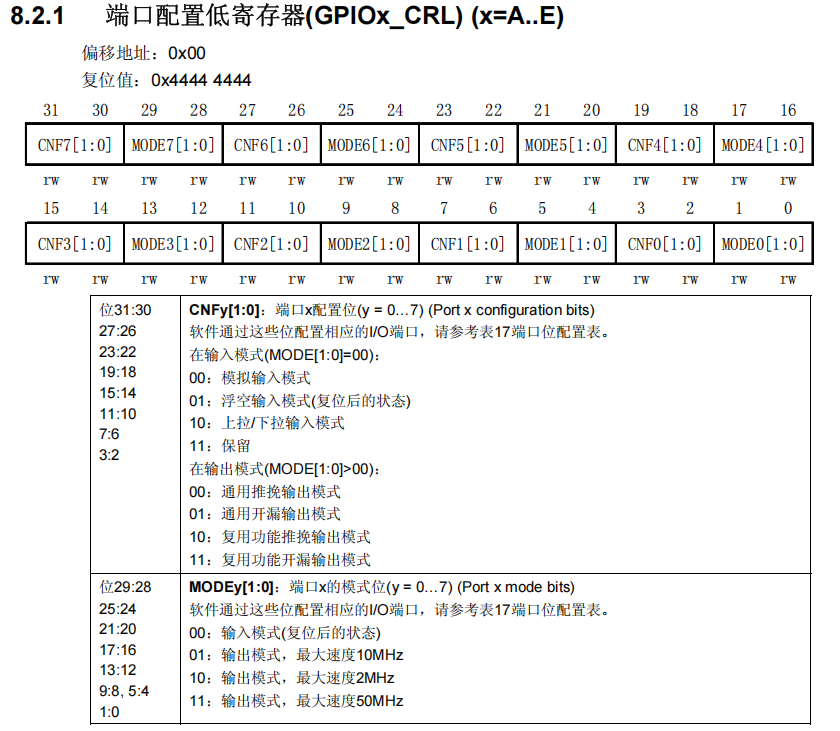

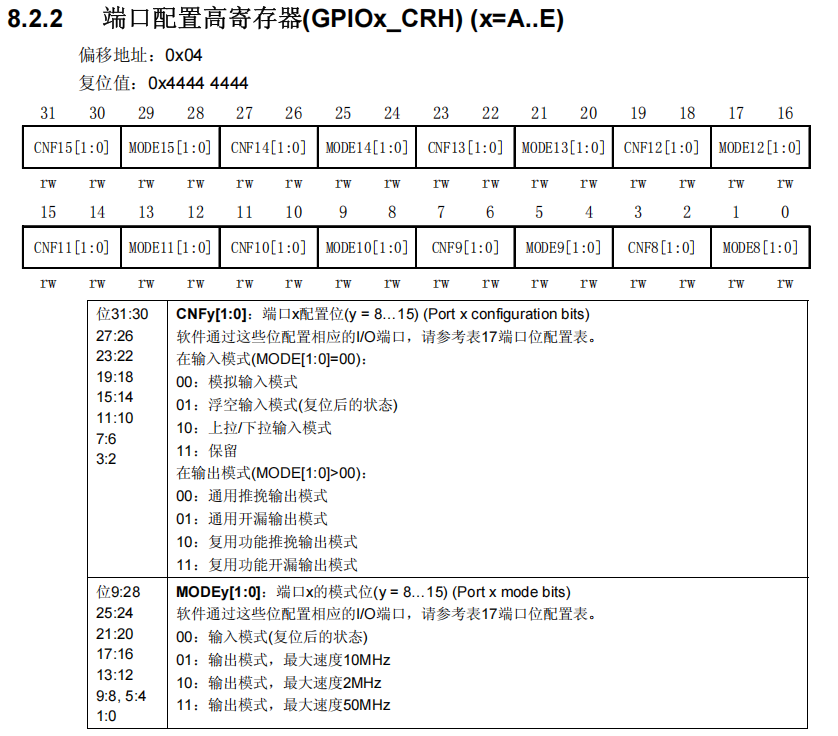

4.1 端口配置 高、低 寄存器(Configuration Register Low/High)

此俩寄存器用于配置 IO 口的 工作模式和输出速度。

一组 IO 有16个,高、低寄存器每四个bit(CNFy、MODEy)配置一个IO,两个寄存器64bit,共配置16个IO。

当配置 bit 0b1000, 按配置是 上拉/下拉 输入模式,但不能确定上拉还是下拉,还需要ODR寄存器进行设置。

具体CR配置如下截图。

GPIOx_CRL

GPIOx_CRH

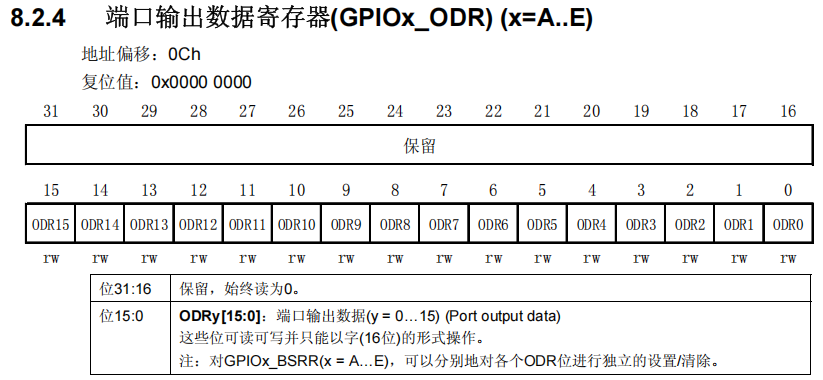

4.2 端口输出数据寄存器(Out Data Register)

GPIOx_ODR

16个 bit 对应16个IO。用于设置IO引脚输出时的高低电平。

还可通过此寄存器配置上拉/下拉输入配置。

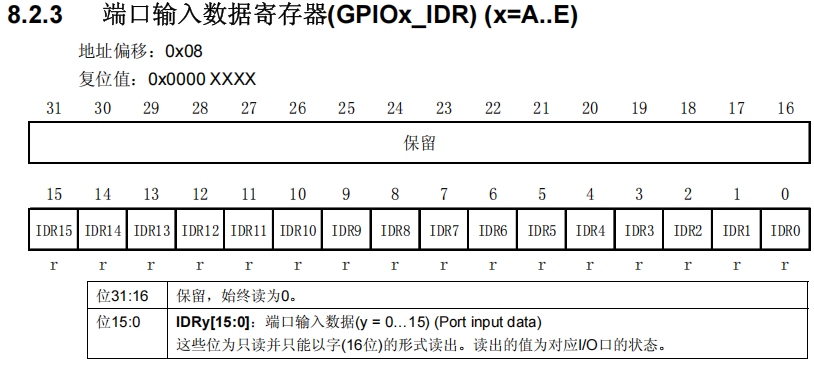

4.3 端口输入数据寄存器(Input Data Register)

GPIOx_IDR

只读,读取对应 IO 的状态,用于判断引脚电平。

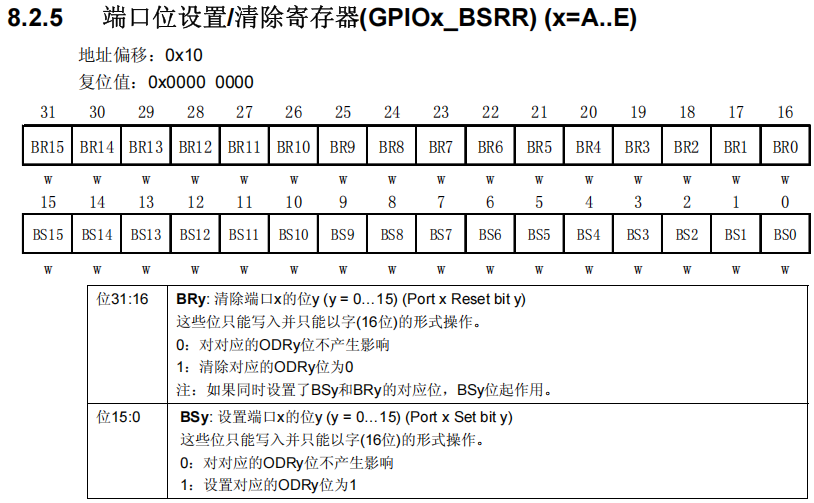

4.4 端口位设置/清除寄存器(Bit Set Reset Register)

GPIOx_BSRR

高16bit,写 1 清除ODR寄存器对应bit为0,写0无影响。

低16bit,写 1 清除ODR寄存器对应bit为1,写0无影响。

此寄存器用于控制 ODR寄存器

4.5 不建议使用的寄存器

GPIOx_BRR

GPIOx_LCKR

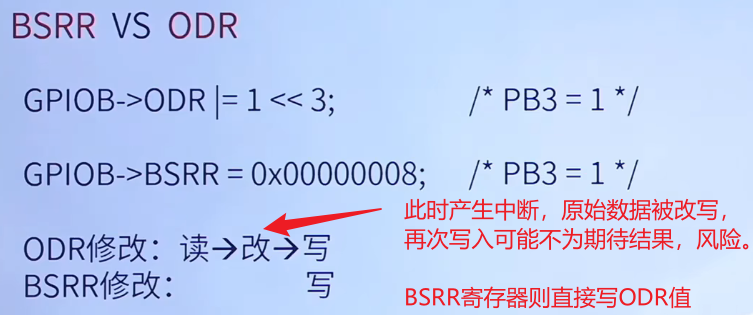

4.6 ODR 与 BSRR*

![]()

![]()

类似C中 volatile关键词,从原始地址获取值,以防缓存值与原始值不一致。

的3D GPR数据分析)