一、铺垫引入中断 → 按键

1、概要:

实现按键控制发光二极管和蜂鸣器

输入类型的外设:按键(key)

2、参考手册内容完成配置过程

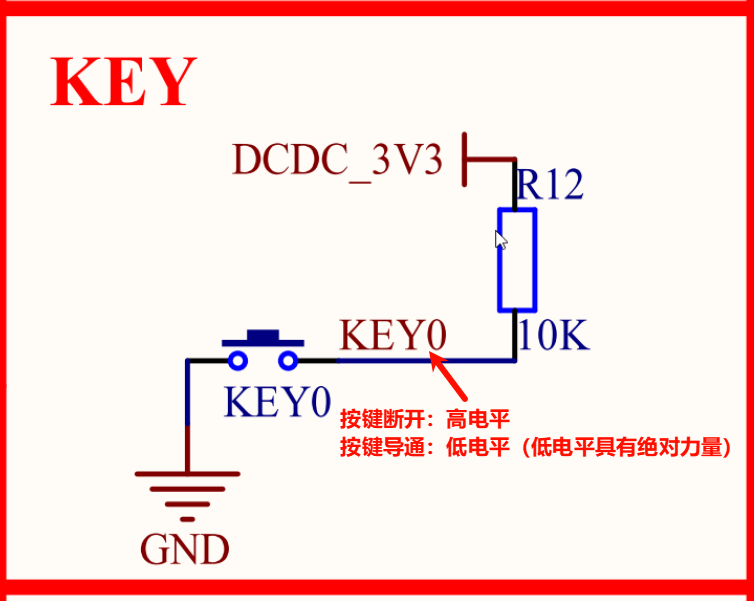

(1)key 按键原理图

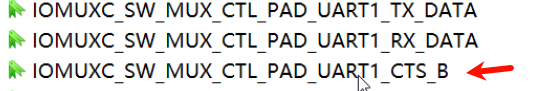

(2)core 内核中命名 -- UART1 CTS

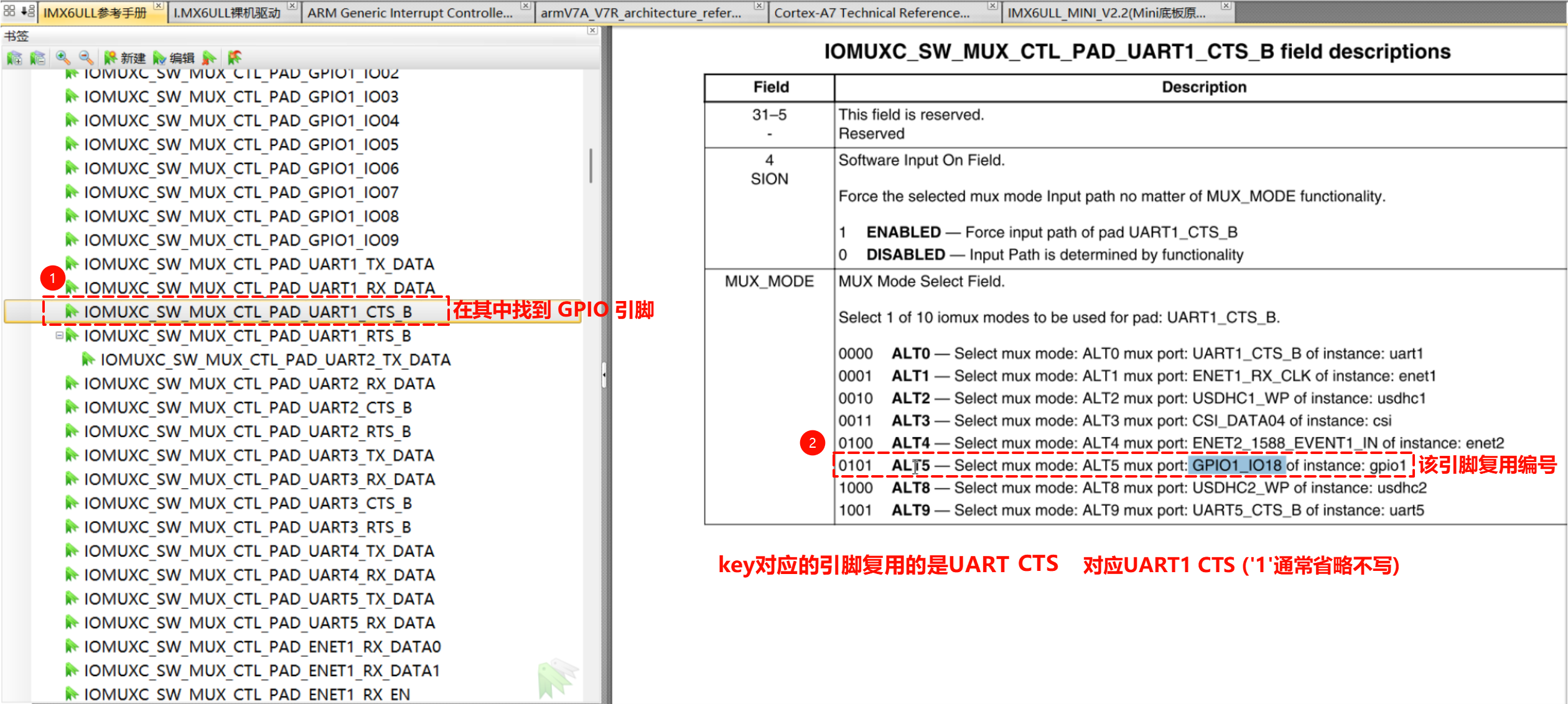

(3)复用功能设置

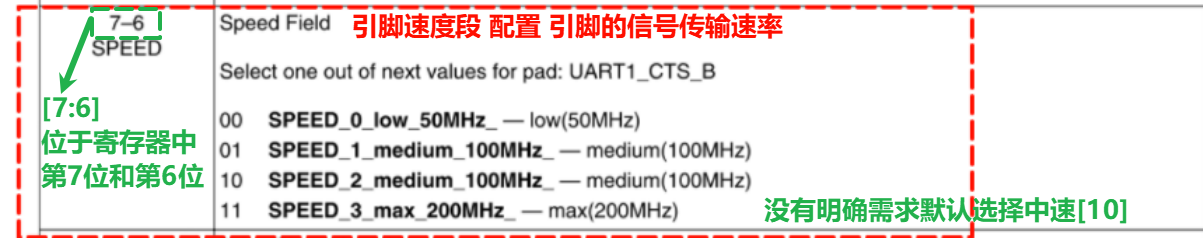

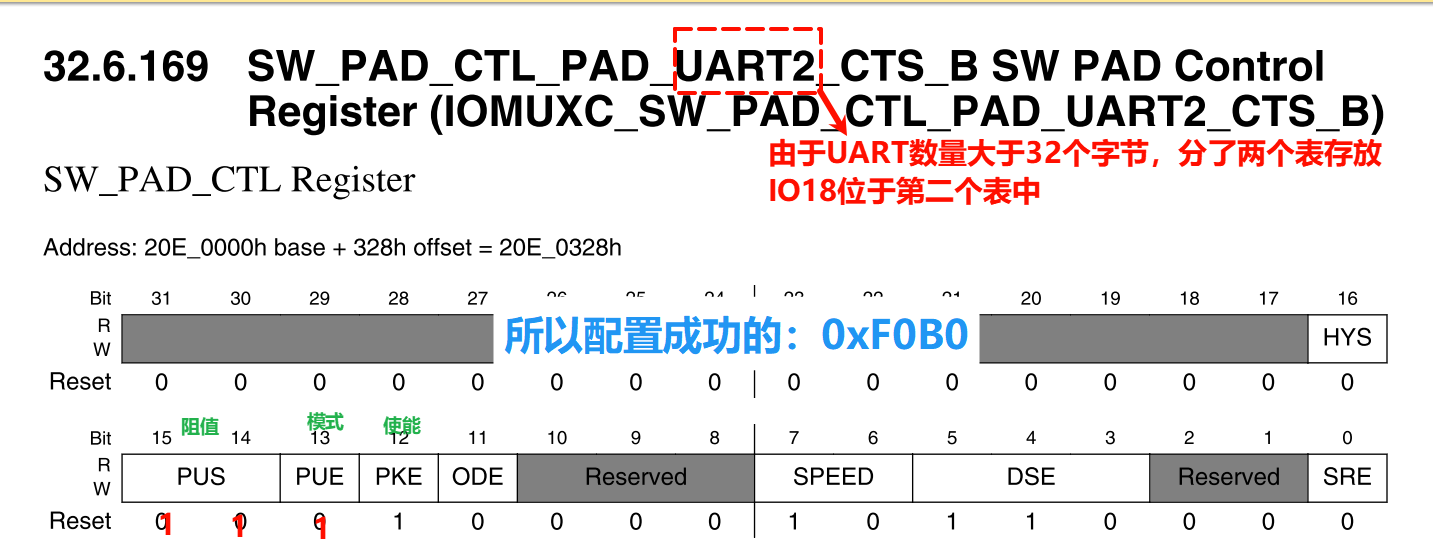

(4)电气特性配置

一般顺序:12 - -> 13 - -> 14-15

阻值不明确时通常选择10K,如若没有选择阻值相近于10k的(所以选择22k的[11])

1)上拉电阻

2)速率

3)综合

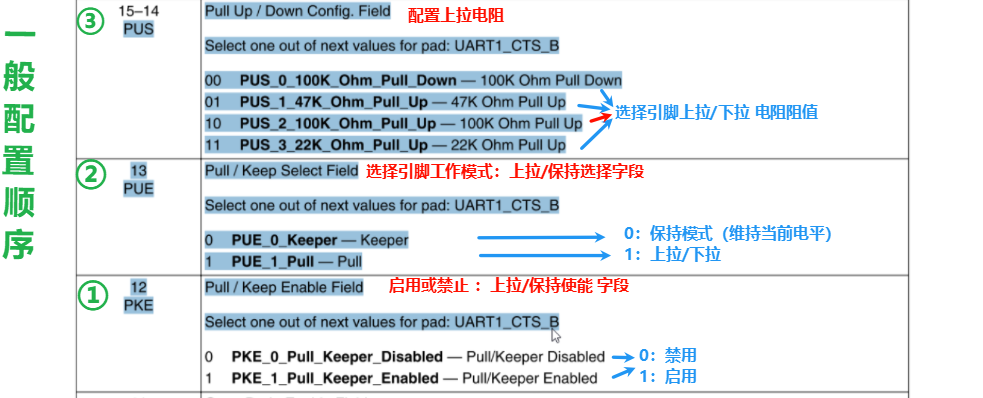

(5)引脚方向配置

GPIO1->GDIR &= ~(1 << 18); //仅需要将GPIO的第18号引脚 置1

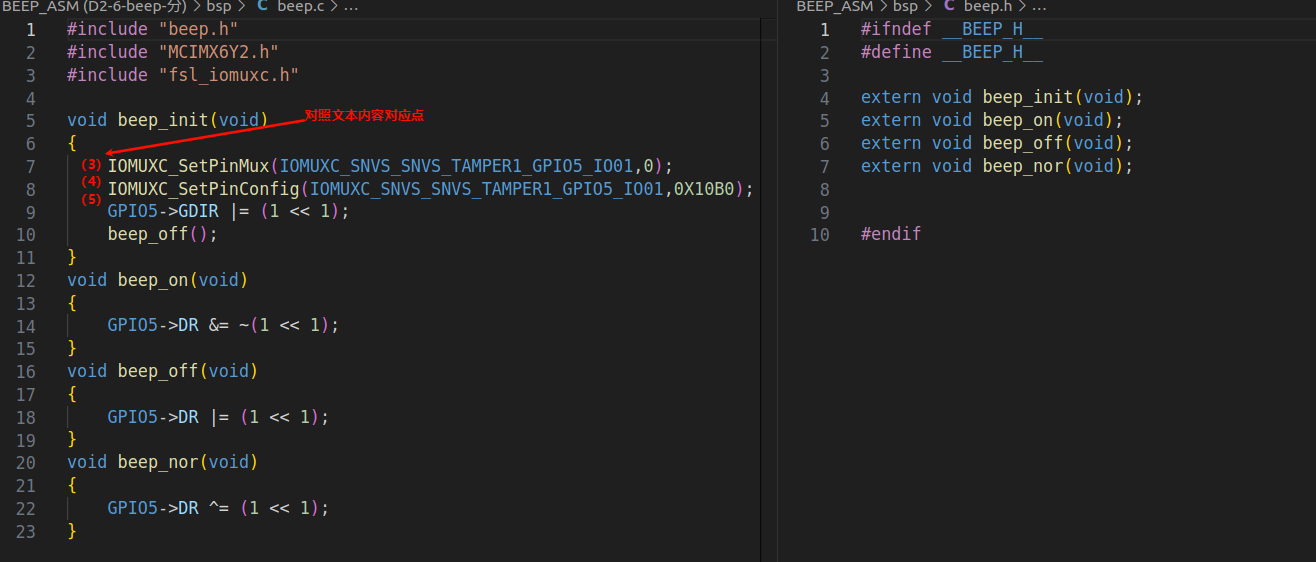

3、代码实现

4、实验现象

能够实现按下按键是,蜂鸣器响应,led亮。但是会出现按下按有时无法立刻响应,是由于现有模式是轮询模式,cpu无法在按键按下时就立刻进行响应,也许在你按下按键时刻,cpu正在别的地方检测,所以会出现延时性。

由此引出,引入中断。当按下按键时刻,能够立刻响应。中断:cpu在轮询中有更为紧要的事情打断,保护现场,去执行中断任务,当执行完毕后,回到现场,恢复形成继续进行刚刚被打断前的任务。

二、中断的引入

1、概念

中断:CPU能打断当前正在进行的工作,去处理更为紧急的任务,并且在处理完中断任务后,能回到原先的地方继续工作

2、流程

(1)中断源发出中断请求。

(2)CPU检查是否响应中断以及该终端是否被屏蔽。

(3)检查当前产生的中断的中断优先级。

(4)保护现场

(5)执行中断服务函数

(6)恢复现场

3、流程图

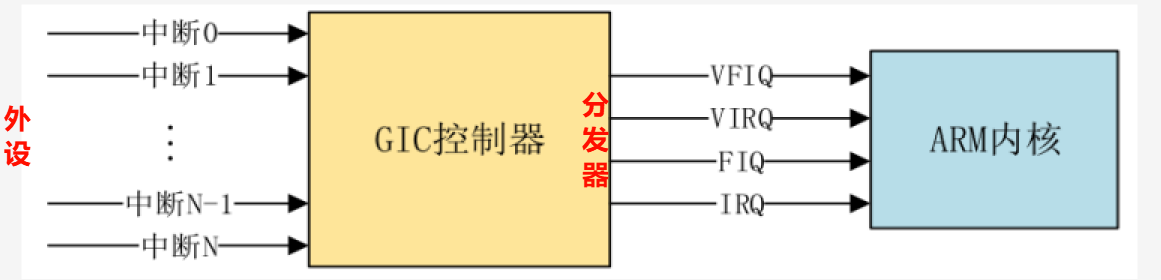

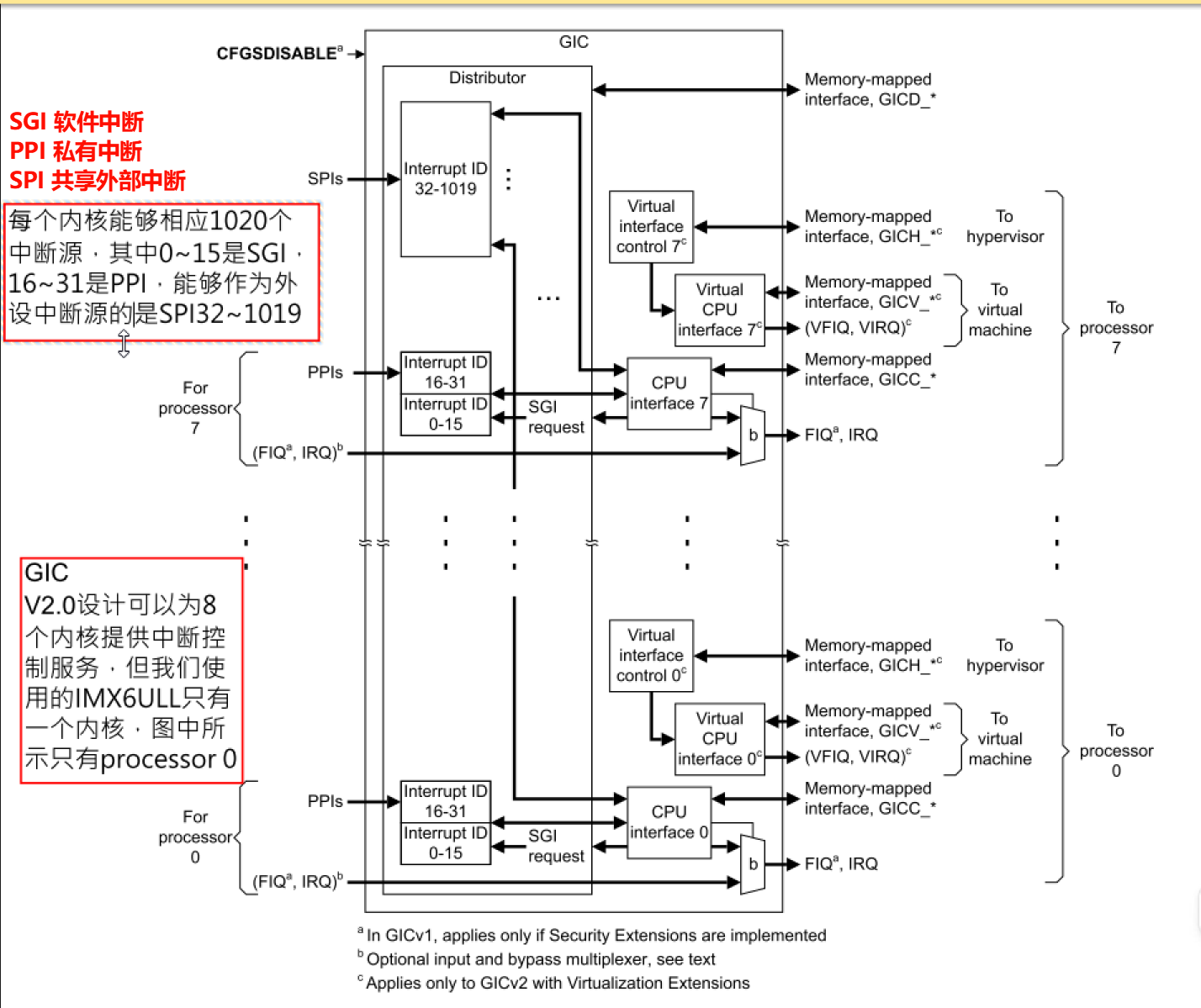

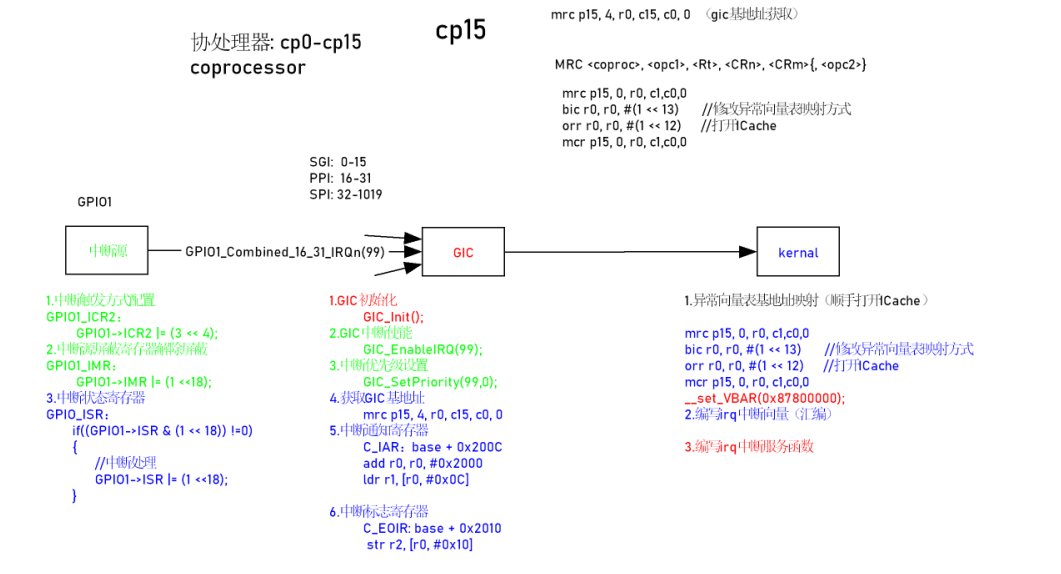

由下图可知:想要实现中断还需要GIC控制器作为中间桥梁进行传递(秘书处)

(1)中断基本流程

(2) 三类分发器 SGI、PPI、SPI

4、中断控制器GIC

(1)概念

ARM处理器中管理中断的硬件模块,负责接收外设中断请求(IRQ),根据优先级、目标核和安全属性分发到CPU核心;

(2)类型

SGI(Software Generated Interrupt):核间通信中断(ID0-15),通过写寄存器,触发由软件触发引起的中断,通过向寄存器GICD_SGIR 写入数据来触发,系统会使用 SGI 中断来完成多核之间的通信

PPI(Private Peripheral Interrupt):核私有中断(ID16-31),如定时器中断,我们说了 GIC 是支持多核的,每个核肯定有自己独有的中断。这些独有的中断肯定是要指定的核心处理,因此这些中断就叫做私有中断

SPI(Shared Peripheral Interrupt):共享外设中断(ID32-1019),如GPIO、UART中断,(注意!不是 SPI 总线那个中断),这类中断泛指所有的

(3)功能

中断触发、优先级仲裁、CPU响应、中断完成

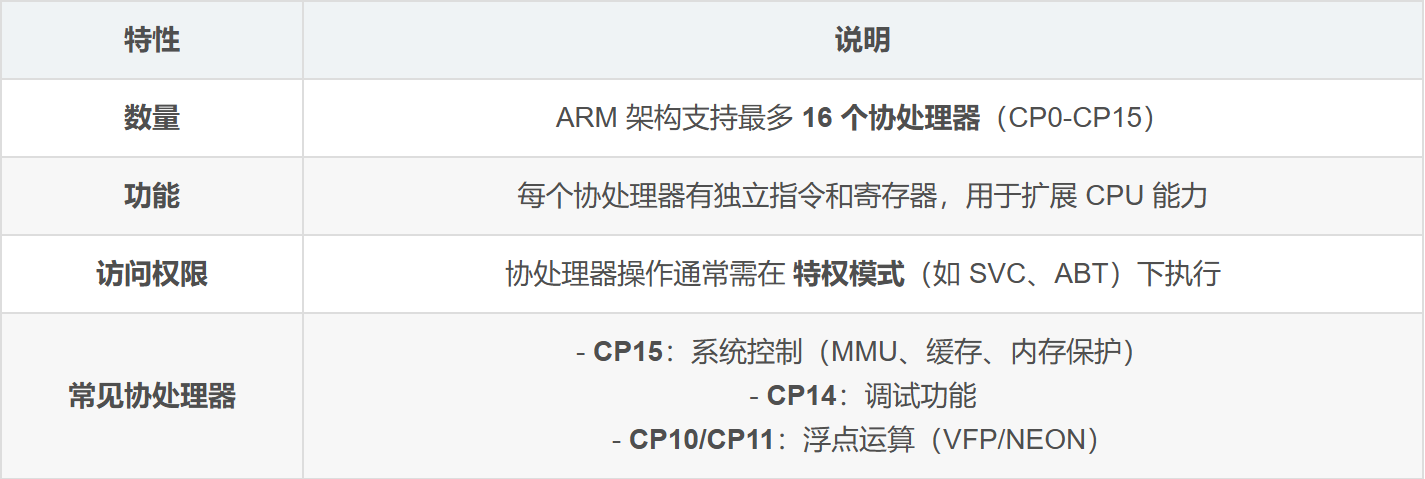

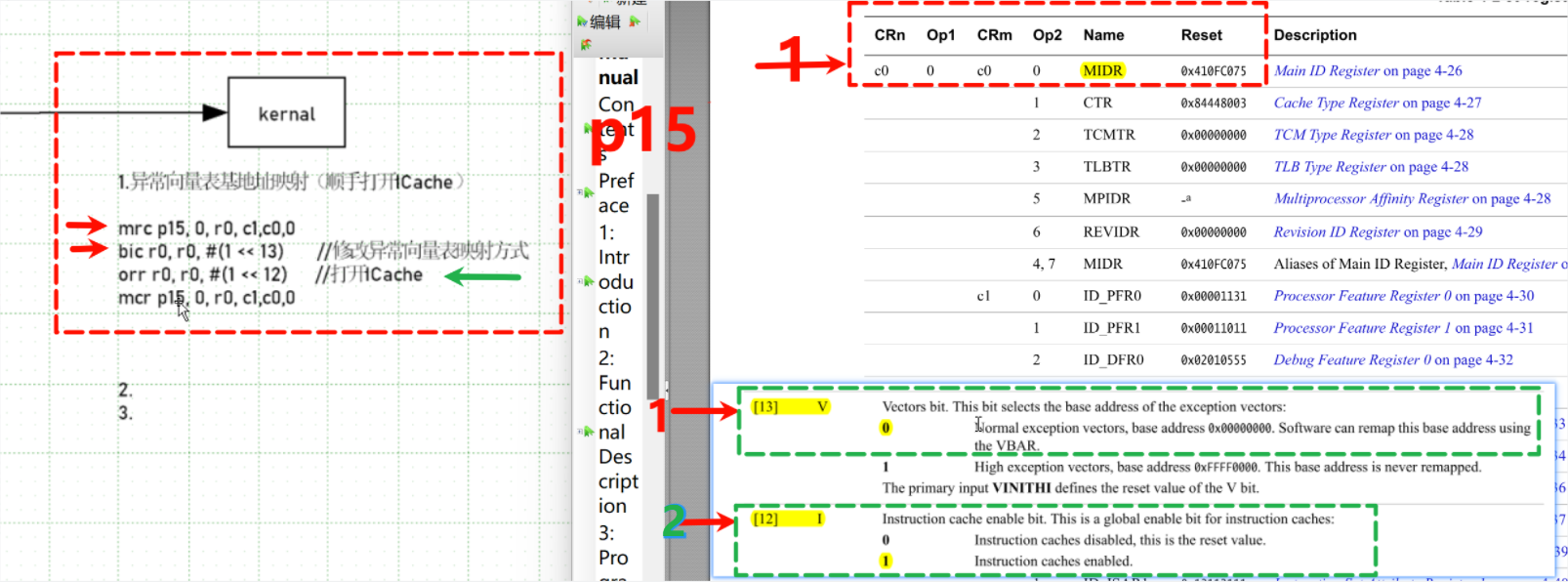

5、协处理器:cp0 - cp15

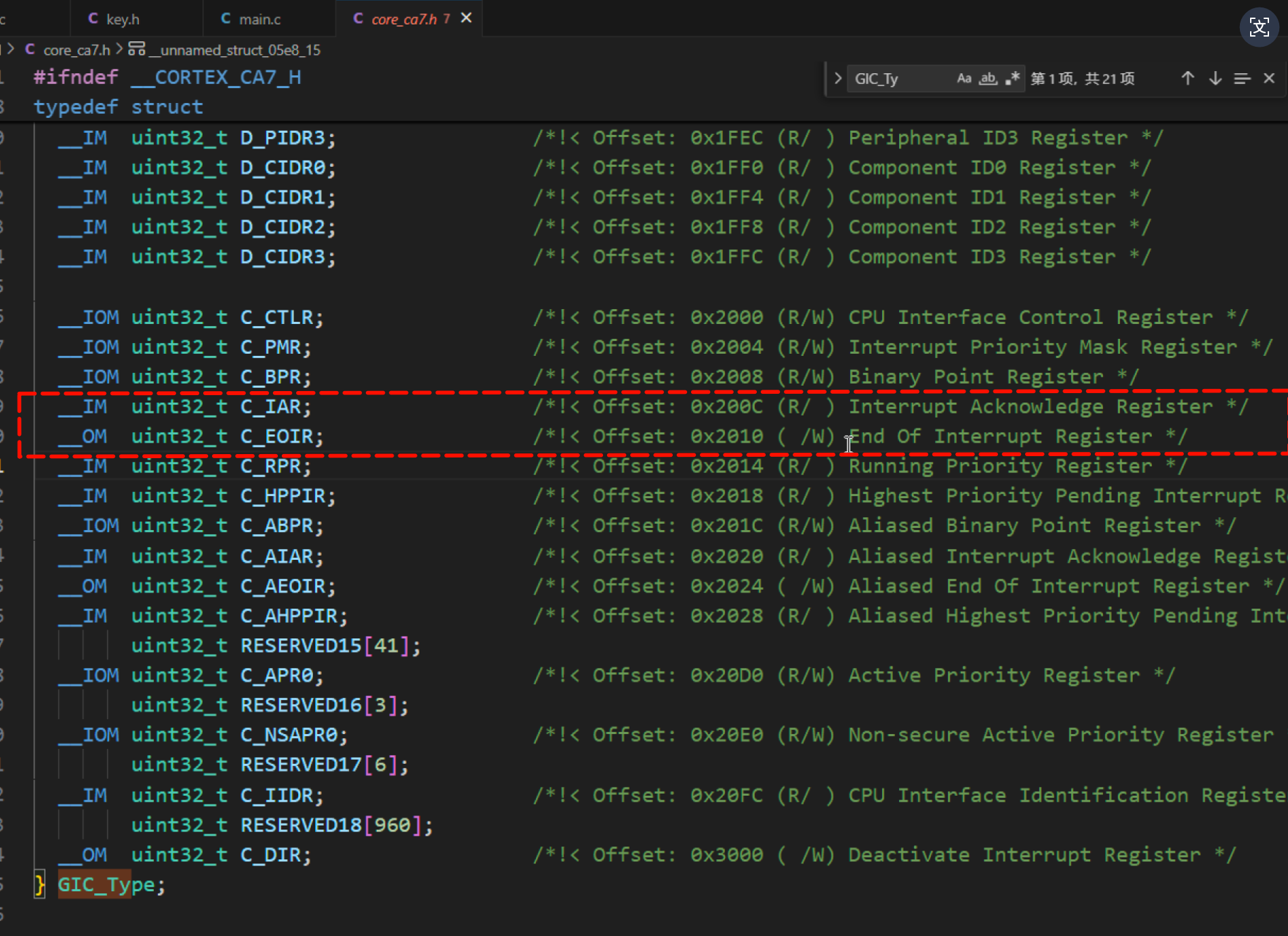

内核中的用到的ARM Cortex-A7内核GIC(通用中断控制器)的关键寄存器

C_IAR

- 全称:Interrupt Acknowledge Register(中断应答寄存器)

- 功能:读取时返回当前最高优先级的中断ID,表示处理器已接受该中断

- 访问权限:只读(

__IM)- 偏移地址:

0x200CC_EOIR

- 全称:End Of Interrupt Register(中断结束寄存器)

- 功能:写入中断ID以通知GIC中断处理完成

- 访问权限:只写(

__OM)- 偏移地址:

0x2010无法直接知道基地址,引入协处理器- GIC的地址保存在协处理器的cp15中

(1)协处理器概念

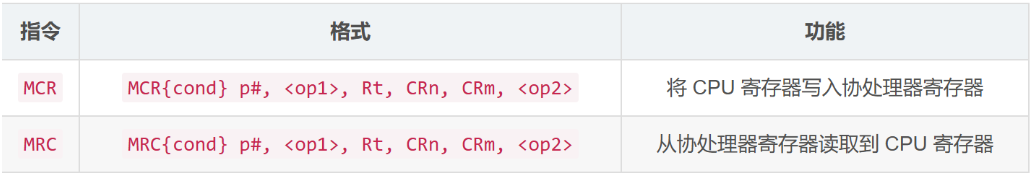

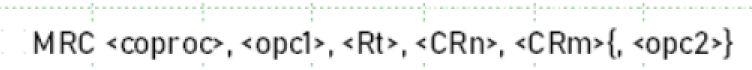

(2)核心指令

cond:省略表示无条件执行。p15:指定协处理器 CP15(系统控制协处理器)。opc1:操作码1,此处为0(CP15 规定opc1必须为 0,否则结果不可预测)。Rt:目标寄存器,示例中为r0(ARM 核心寄存器)。CRn:协处理器主寄存器编号,示例中为c0。CRm:附加寄存器或操作数,示例中为c0(若无需附加信息,通常设为c0)。opc2:次要操作码,示例中为0(用于区分同一编号寄存器的不同功能)

示例:

eg:MRC p15, 0, r0, c0, c0, 0

// 指令从 CP15 的

c0寄存器(主标识符寄存器)读取数据到 ARM 的r0寄存器。c0是只读寄存器

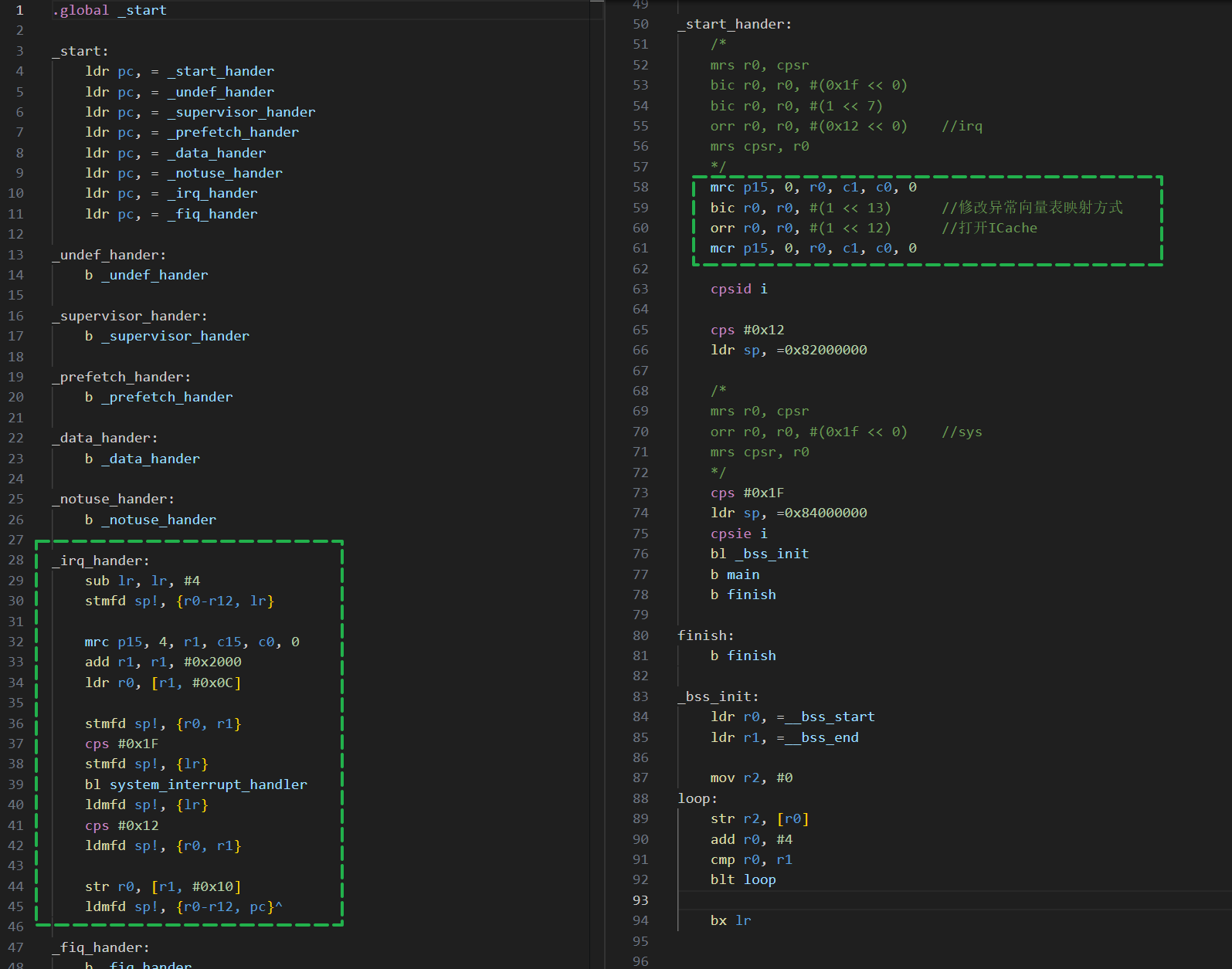

(3)异常向量表基地址的配置实现过程

6、详细蓝图

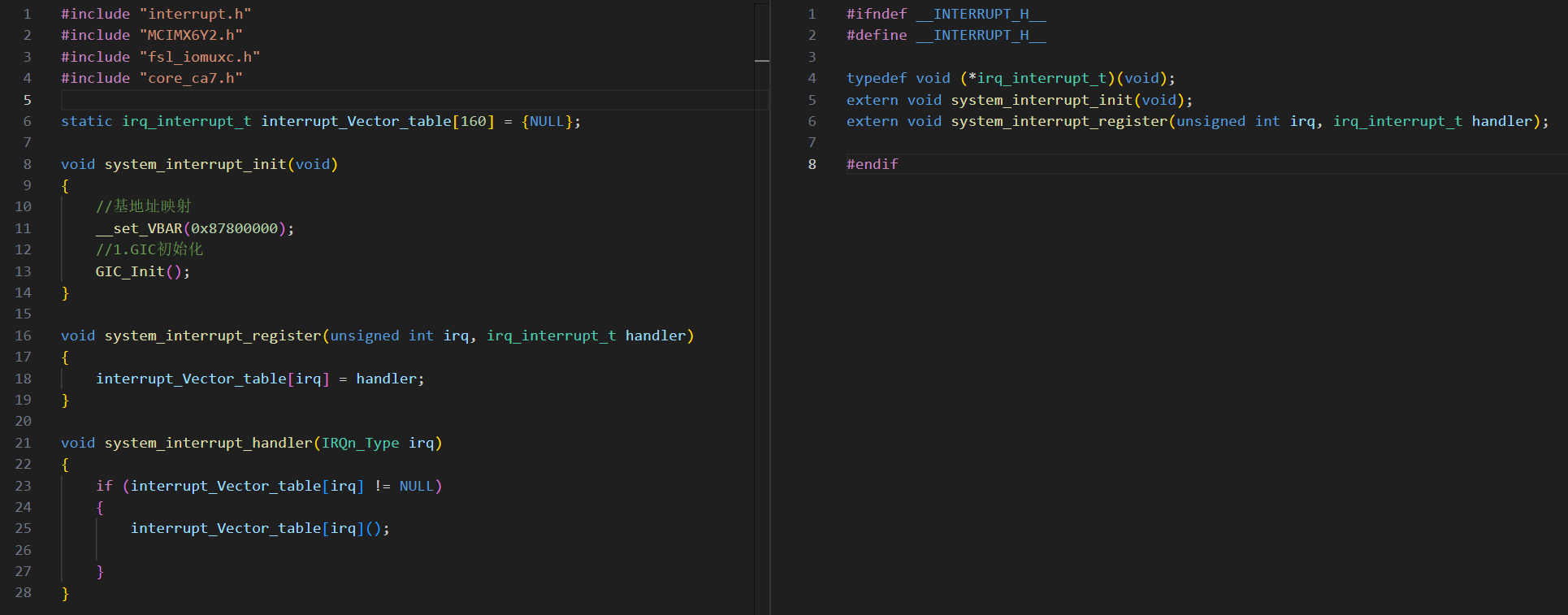

7、代码实现

interrupt.c interrupt.h

start.S

)

打开工程文件的几种方法)

:2.点灯与ubuntu安装)

》)