第 5 章IJTAG 网络插入

IJTAG 网络插入功能使您能够连接现有的instrument,并插入 SIB、TDR 和 ScanMux 以创建您自己的 IJTAG 网络。 IJTAG 网络插入功能使您能够将网络连接到 TAP 控制器或设计中已有的 TAP 控制器。IJTAG 网络插入的原理是使用 create_dft_specification 命令,非常简单。工具读取设计中instrument的 ICL 模型,并根据 ICL 模型的访问需求插入 SIB 或 TDR。如果需要,您可以编辑或修改 IJTAG 网络以满足设计需求。 完成设计编辑后,您可以使用 extract_icl 命令生成 IJTAG 网络的 ICL 描述。请注意,工具在 IJTAG 网络插入后不会自动执行 ICL 提取,因为您可以在提取前进行额外的编辑。 Tessent IJTAG 可以生成并连接自己的 TAP,也可以连接到已有的 TAP 控制器。如果 IJTAG 网络需要连接到已有的 TAP 控制器,则必须提供该 TAP 控制器的 ICL。

IJTAG 网络插入流程

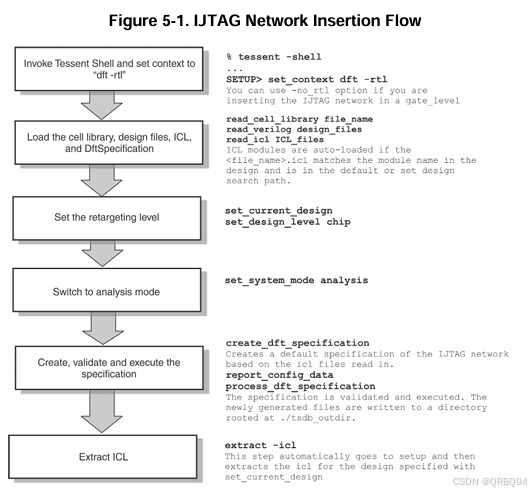

本节介绍了基本的 IJTAG 网络插入流程,并列出了实现该流程的相应命令。 图 5-1 展示了您使用 Tessent Shell 执行的基本 IJTAG 网络插入流程的步骤。

如图 5-1 所示,IJTAG 网络插入流程相对简单。由于您需要修改设计文件,因此必须将工具设置为 DFT 上下文,然后加载单元库、设计文件以及所有使用的instrument的 ICL(这些可以自动为您加载)。第一个 create_dft_specification 命令指示工具创建 DftSpecification,第二个命令 process_dft_specification 在生成并修改设计文件之前运行一个验证步骤。 当工具处理 DftSpecification 时,它会将文件写入磁盘上的有组织的目录结构中。这些文件包括以 ICL 和 Verilog 格式表示的所有插入的 IJTAG 网络对象(SIB、TDR 和 ScanMux)以及所有修改后的设计文件。IJTAG 网络是使用 create_dft_specification 命令自动生成的。然而,您始终可以使用编辑命令或通过使用 display_specification 的 GUI 来修改创建的 DftSpecification。如前所述,网络的 ICL 描述不会自动生成,因为您可能需要进行进一步的设计编辑。然而,由于所有数据都存储在内存中,您可以使用 extract_icl 命令执行后续的 IJTAG 网络提取步骤。

IJTAG 网络插入示例

以下是一个 IJTAG 网络插入的示例。

set_context dft -no_rtl

## 读取库

read_cell_library ./library/adk_complete.tcelllib

read_cell_library ./library/memory.atpglib

## 读取网表

read_verilog ./netlist/cpu_top_scan_tk.v

read_verilog ./generated/cpu_top_edt.v

read_verilog ./PLL/PLL.v -interface_only

## 在 set_current_design 之前读取 ICL 和 PDL 文件

read_icl ./PLL/PLL.icl

dofile ./PLL/PLL.pdl

set_current_design cpu_top

## 在运行 set_system_mode analysis 之前设置设计级别

set_design_level chip

## 使用 set_attribute_value 指定 TAP 引脚

set_attribute_value tck_p -name function -value tck

set_attribute_value tdi_p -name function -value tdi

set_attribute_value tms_p -name function -value tms

set_attribute_value trst_p -name function -value trst

set_attribute_value tdo_p -name function -value tdo

set_system_mode analysis

report_icl_modules

## 自动从读取 Verilog 的目录中读取任何 ICL

create_dft_specification

report_config_data

## 使用 display_specification 编辑或修改规范,或者使用编辑命令(如果需要)

## 如果需要的话。

process_dft_specification

extract_icl

exit

上述示例首先将context设置为 dft 并读取库。 下一步是读取已经插入扫描和 EDT IP 的 Verilog 网表,其中 PLL 模块已经存在。对于 PLL 模块,已经单独创建并验证了 ICL 和 PDL。接下来读取 PLL 的 PDL 和 ICL。使用 set_design_level 指定插入 IJTAG 网络的级别。在此示例中,IJTAG 网络插入在设计的顶层,因此在运行“set_system_mode analysis”之前指定了 TAP 引脚。 通过 create_dft_specification,PLL 和 EDT instrument的 ICL 自动配置为插入到 IJTAG 网络中。可以使用 report_config_data 报告此网络。如果需要 IJTAG 网络连接,则使用 process_dft_specification,否则使用编辑命令或与 Configuration Data Visualizer 一起使用的 display_specification 来编辑。最后一步是 extract_icl,它为使用 set_current_design 设置的级别提供 ICL。

布局感知的 IJTAG 连接

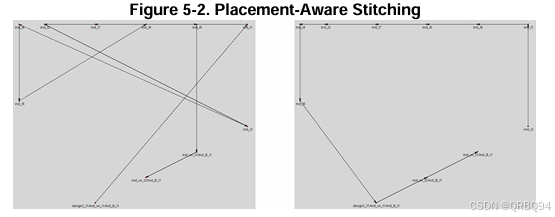

布局感知的 IJTAG 连接功能通过使用 DEF 文件中的坐标来创建节点之间的最短路径,从而改善 IJTAG 扫描链中元素的排序。 如果没有布局信息,工具会按字母顺序将每个层次级别的签核模块和 IJTAG instrument连接到一个 IJTAG 链中。按字母顺序连接可能导致布局和布线问题,但布局感知连接有助于缓解这一问题。 图 5-2 比较了按字母顺序连接(左侧)和布局感知连接(右侧)的 IJTAG 网络布局示例。

布局感知连接使用 DEF 文件中的坐标生成一个 DftSpecification 包装器,该包装器对 IJTAG 元素进行排序以创建节点之间的最短路径。加载 DEF 文件时,布局感知处理是自动进行的(不需要特殊的命令或开关)。DEF 文件应提供 IJTAG instrument扫描输出引脚的布局信息。如果扫描输出引脚的坐标缺失,布局感知连接将使用实例坐标。 连接从 IJTAG 扫描输出端口(ijtag_so 或 tdo)开始。工具确定哪个元素的布局位置最近,并将其作为下一个节点,直到所有元素都连接到链中。如果扫描输出端口的坐标缺失,连接将从坐标最接近(0,0)点的元素开始。 注意 您也可以通过在 Tessent Shell 中设置 “def_x_coordinate” 和 “def_y_coordinate” 属性来提供节点坐标。

修改 IJTAG 网络插入流程

在大多数使用场景中,您可以使用基本的 IJTAG 网络插入流程。然而,如果需要,您可以对流程进行以下修改。

表 5-1. IJTAG 网络插入流程的修改

要... | 描述 |

更改输出目录根目录 | 默认情况下,process_dft_specification 命令将所有编辑后的设计文件和生成的 IJTAG 网络对象文件写入以 ./tsdb_outdir 为根目录的有序目录结构中。您可以使用 set_tsdb_output_directory 命令指示工具使用任何其他目录根目录;如果该目录尚不存在,工具将创建它。 |

验证写入的 DftSpecification 是否正确 | 您有多种选项可以验证写入的 DftSpecification 是否正确。请参阅 process_dft_specification 命令的“-no_insertion”和“-validate_only”选项。 |

转录所有执行的设计编辑 | 高级命令 process_dft_specification 运行一系列 Tessent Shell 编辑命令,例如 create_connections 或 create_instance。通常,这些命令不会被转录,但在调试时可能很有用。process_dft_specification 命令为您提供 -transcript_insertion_commands 选项,该选项将 DftSpecification 执行期间执行的所有设计编辑步骤添加到转录中。 |

运行 DftSpecification | 您可以为当前设计加载多个 DftSpecification;它们根据用户指定的标识符有所不同。有关更多信息,请参阅 DftSpecification 包装器描述。通过 process_dft_specification 命令的 “id” 选项,可以轻松选择其中一个或另一个 DftSpecification。 |

自动运行额外的设计编辑 | 在 DftSpecification 处理结束时,修改后的设计文件将写入输出目录。如果您想进一步编辑设计,自动写入设计文件是一个不必要的且可能耗时的步骤。process_dft_specification 命令提供了一种方法,告诉工具在写入最终的修改后设计文件之前,先运行您的设计编辑命令。然后,该文件将包含插入的 IJTAG 网络以及您指定的设计编辑。 |

写入 process_dft_specification.post_insertion 过程 | 如果您正在编写一个名为 process_dft_specification.post_insertion 的特定名称的 Tcl 过程,并将其加载到内存中,您可以使用 dofile 命令并针对包含此过程的文件。或者,您也可以直接在主 dofile 中编写 Tcl 过程。当 process_dft_specification 命令看到存在 Tcl 过程时,它将在 DftSpecification 指定的所有设计编辑成功完成后,但在运行 write_design 命令之前,自动调用 Tcl 过程。 |

- mtk_pd_adapter.c)

基本了解和工程配置)

LED 驱动芯片:特性与应用)

优化函数(付完整代码))

算法详解)

![[特殊字符] 认识用户手册用户手册(也称用户指南、产品手册)是通过对产品功能的清](http://pic.xiahunao.cn/[特殊字符] 认识用户手册用户手册(也称用户指南、产品手册)是通过对产品功能的清)