TAP的作用

tap全称是test access port,是将jtag接口转为reset、sel、ce、ue、se、si、tck和so这一系列测试组件接口的模块。

jtag的接口主要是下面几个信号:

| 信号名称 | 信号方向 | 信号描述 |

|---|---|---|

| TCK(测试时钟) | 输入 | 测试时钟,同步JTAG状态机和数据移位操作。 |

| TMS(测试模式选择) | 输入 | 测试模式选择,控制JTAG TAP(Test Access Port)状态机 的转换。 |

| TDI(测试数据输入) | 输入 | 测试数据输入,用于向芯片的JTAG逻辑串行输入测试指令或数据。 |

| TDO(测试数据输出) | 输出 | 测试数据输出,用于从芯片的JTAG逻辑串行输出测试结果或状态。 |

| TRST(测试重置) | 输入 | 可选信号,用于重置 TAP 控制器的状态机,低电平有效。如果没有该信号,也可通过 TMS 对 TAP 控制器进行复位。 |

上面的信号才是Jtag的接口信号,每一个信号都对应一个IOPAD。在设计中常会遇见tdo_en信号,这个信号是控制IOPAD在没有输出时,输出高阻态。它并不是实体的IO信号。也有可能会遇见tdi_en信号,控制IOPAD没有输入时,输入为高阻。单一般不会控制IOPAD的输入。

那么TAP就是把这些Jtag接口,主要是通过解析TMS的指令来生成以下组件控制信号。

| 端口 | 方向 | 全称 | 功能描述 | 时序 |

| reset | 输入 | Reset | 异步或同步复位信号,用于初始化DFT逻辑(如扫描链)。 | 复位时立即生效,扫描链寄存器被清零或置位。 |

| sel | 输入 | Select | 选择测试模式或功能模式: `sel=1` → 测试模式(扫描链激活) `sel=0` → 功能模式 | 通常在测试开始时拉高,测试结束时拉低。 |

| ce | 输入 | Capture Enable | 控制扫描链捕获功能逻辑数据: `ce=1` → 捕获数据 `ce=0` → 保持或移位 | 在 `tck` 的上升沿生效。 |

| ue | 输入 | Update Enable | 控制扫描链数据更新到功能逻辑: `ue=1` → 更新数据 `ue=0` → 保持 | 通常在 `tck` 的下降沿生效(取决于设计)。 |

| se | 输入 | shift Enable | 控制扫描链模式: `se=1` → 移位模式(数据从 `si` 移入) `se=0` → 捕获模式 | 在 `tck` 的上升沿生效。 |

| si | 输入 | Scan Input | 扫描链的串行输入数据,用于移入测试向量。 | 在 `tck` 的上升沿采样,数据逐位移入扫描链。 |

| from_so | 输入 | From Scan Output | 来自另一条扫描链的串行输出(用于多扫描链级联)。 | 类似 `si`,但数据来自其他扫描链的 `so`。 |

| tck | 输入 | Test Clock | 测试时钟,独立于系统时钟,控制扫描链的移位和捕获操作。 | 上升沿用于移位/捕获数据,下降沿可能用于更新(如 `ue`)。 |

| so | 输出 | Scan Output | 扫描链的串行输出,用于移出测试响应数据。 | 在 `tck` 的上升沿或下降沿(取决于设计)输出扫描链的最后一位数据。 |

TAP的使用场景

大多数芯片采用 单 TAP + SIB(Scan Insertion Buffer) 的层次化架构,而非为每个 harden 分配独立 TAP:

单 TAP 控制所有 IP

-

芯片只有一个 顶层 TAP(遵循 IEEE 1149.1 JTAG 或 IEEE 1687 IJTAG 标准)。

-

通过 SIB(Scan Insertion Buffer) 动态选择访问不同 harden 的扫描链。

-

优点:节省面积、简化测试接口、兼容标准 JTAG 调试工具。

特殊情况:多 TAP(较少见)

某些场景可能为特定 harden 分配独立 TAP:

-

需求场景

-

安全隔离需求:如安全域与非安全域需物理隔离测试接口。

-

超大规模芯片:多个子系统需并行测试以减少时间。

-

第三方 IP 要求:某些硬核 IP 可能强制要求独立 TAP(如某些 GPU/DSP 核)。

-

-

缺点

-

面积开销:每个 TAP 需额外的 I/O 引脚和控制器逻辑。

-

测试复杂度:需多路复用芯片级 TAP 接口,或增加专用测试引脚。

-

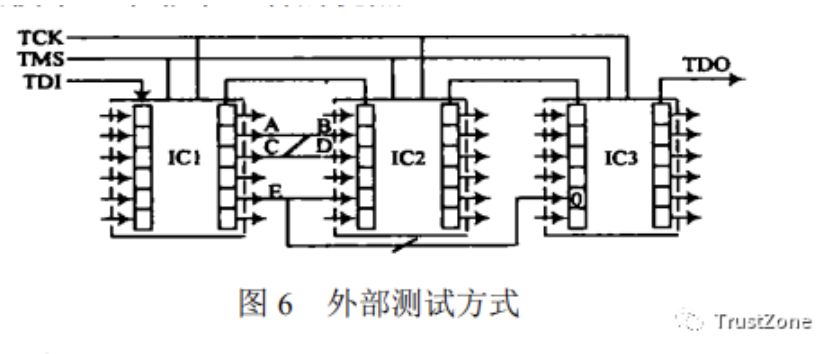

向下图多个chip接成菊花链的形式,实际上就是每个chip里面的tap接成菊花链,当然一个chip内有多个tap也可以这样接,这样就是一个chip内的多个tap共用一套jtag接口,实际上不能实现并行测试,和使用单TAP+SIB的效果是一样的,而且TAP比SIB复杂太多了。如果要保证chip内多个tap能够并行测试,独立测试就需要多组jtag接口。

而且即使是单TAP+SIB,测试多个harden,出了在用jtag配置的时候需要串行【配置一般很快】,patter现在都是走SSN,SSN给多个harden灌patter之后,多个harden就可以并行测试。所以完全没有必要chip内多个tap

单TAP+SIB结构

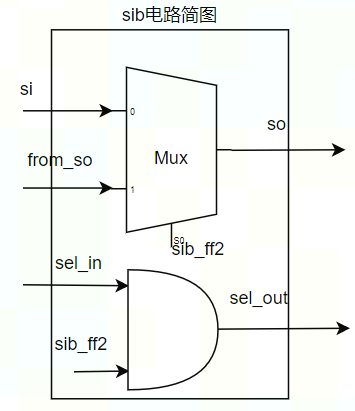

每个sib有一个so输出,和一个sel_out输出。电路简图如下:

其中sib_ff2信号是sib在ue(update_En)时刻锁存的并打2拍信号,而sib是来自se(shift_en)有效时从si或者from_so shift进来的信号锁存。

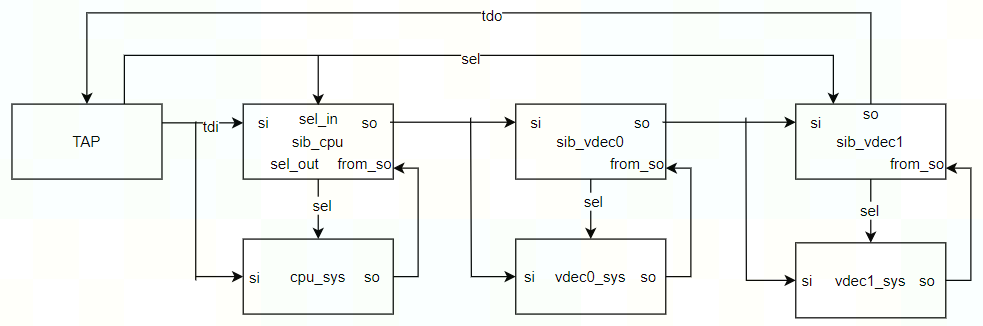

下图给出了一个简单的三个harden级别的TAP+SIB结构

sib_xxx控制着xxx_sys是否在测试菊花链上,相当于一个开关。 在update时候锁存的sib_ff1表示是否bypass当前sib_xxx下的xxx_sys。为1表示不pypass;为0表示bypass。

当sib_ff1=1时:sel_out==1,此时si经过xxx_sys到sib_xxx的from_so在经过sib_xxx的so输出给后级sib和subsys

当sib_ff1=0时:sel_out==0,此时xxx_sys的输入si无法传递,so被sib_xxx bypass。si经过sib_xxx直接经过so传输给下级。

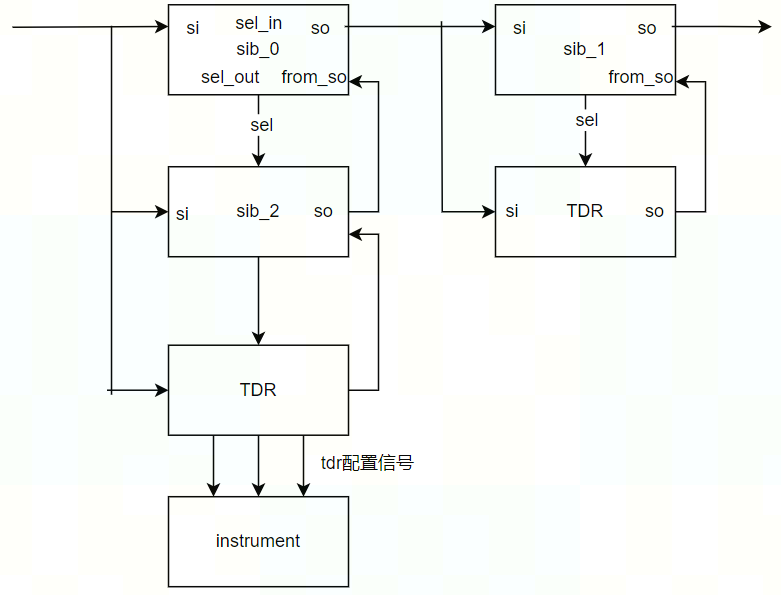

对于subsys测试来说只有si和so这一对输入输出数据线即可。但是subsys内部还可以存在多个sib和tdr组件,但是连接方式和上图类似,如下图的基本结构.具体不在细讲

TDR(Test data register)

主要用于在芯片测试过程中存储、控制和观察测试数据。

和sib的使用类似,或者可以说sib是一个单bit的特殊TDR。

tdr是个多bit的移位寄存器,输入为si,移位输出为so。在ue(updateEn)有效时刻,把tdr中信号锁存为tdr_ff,这个tdr_ff可以用来配置其他寄存器,用作控制作用;在ce时刻可以capture电路的输出响应;在SE时刻可以将测试数据串行或并行加载到电路中。分别描述如下:

1. 存储测试数据

-

TDR 用于临时存储测试输入(测试激励)或测试输出(测试响应)。

-

在 扫描测试(Scan Test) 中,TDR 可以作为扫描链(Scan Chain)的一部分,将测试数据串行或并行地加载到电路中。

2. 控制测试模式

-

在测试模式下,TDR 可以配置芯片的内部逻辑(如切换功能模式到测试模式)。

-

例如,通过 TDR 设置多路选择器(MUX)的输入,选择测试路径或功能路径。

3. 观察测试响应

-

在测试执行后,TDR 可以捕获电路的输出响应,并通过扫描链移出,供外部测试设备(ATE)分析。

-

帮助检测制造缺陷(如固定故障、桥接故障等)。

4. 支持多种测试方法

-

扫描测试(Scan Test):TDR 作为扫描触发器(Scan Flip-Flop)的集合,构成扫描链。

-

内建自测试(BIST):TDR 可能存储 BIST 的种子数据或中间结果。

-

边界扫描(Boundary Scan, IEEE 1149.1 JTAG):TDR 是边界扫描寄存器的一部分,用于测试板级互连。

5. 提高测试灵活性和覆盖率

-

通过动态配置 TDR 的值,可以针对不同模块或故障类型进行针对性测试。

-

支持分片测试(Partitioned Testing),降低测试复杂度。

)