1 PMA

PMA(Physical Memory Attributes),物理内存属性,顾名思义就是用来设置物理内存属性的,但这里说“设置”,并不合理,因为一般情况下各存储的属性,在芯片设计时就固定了,不可动态修改。

1.1 属性定义

PMA定义了物理内存区域的以下静态属性:

-

缓存行为(Cacheable/Non-Cacheable):决定数据是否可被缓存。

-

原子操作支持(Atomics):是否允许使用LR/SC指令进行原子操作。

-

可执行权限(Execute Permission):是否允许执行指令。

例如,外设寄存器通常配置为Non-Cacheable且禁止执行,避免缓存干扰硬件交互;主内存(如RAM)则多设为Cacheable以提升性能。

另外,一般PMA属性在芯片设计时固化,无法通过软件动态修改,需通过硬件逻辑直接实现。这种设计保证了关键内存区域(如外设)行为的确定性,避免运行时误操作。

1.2 SiFive U74 PMA

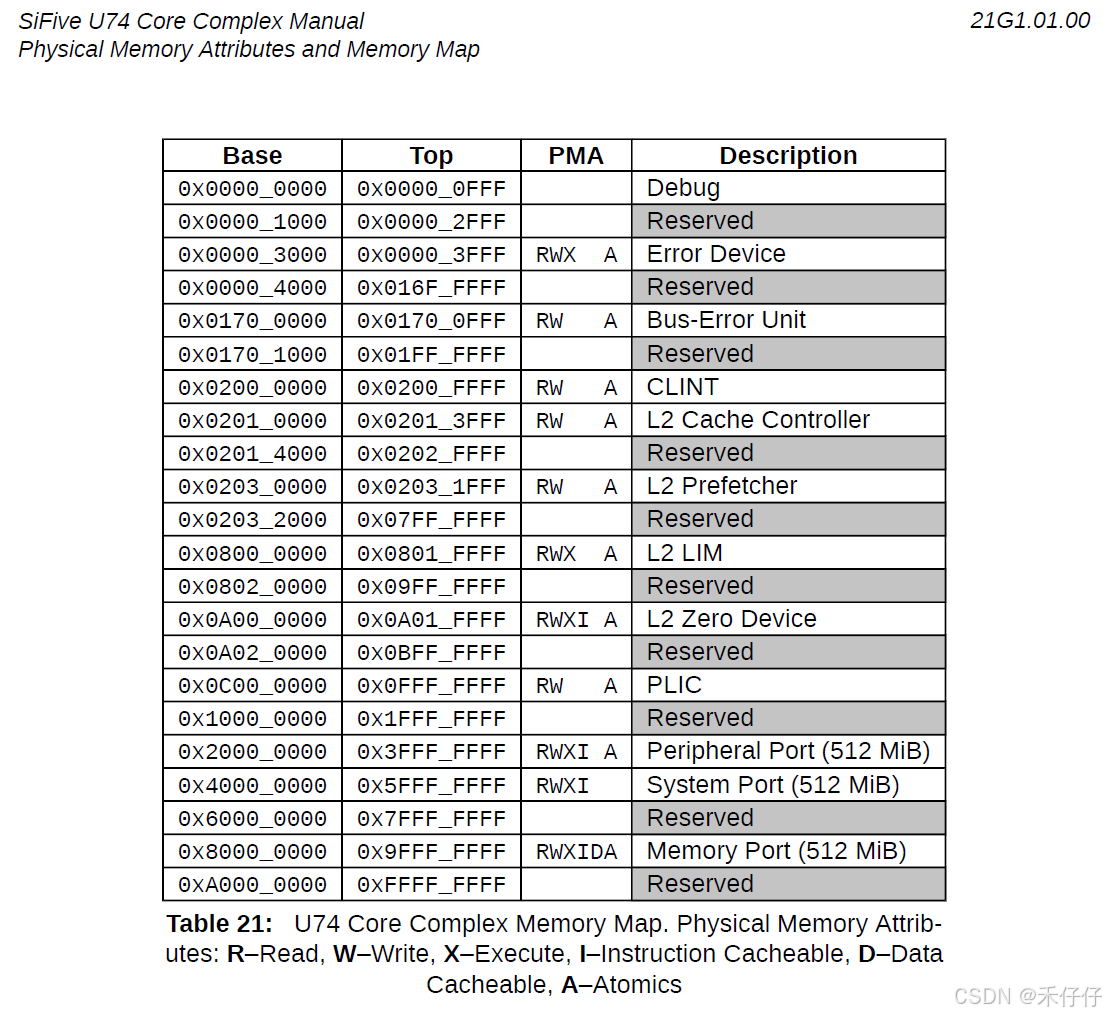

下图是SiFive U74的内存映射和PMA

前面说PMA一般情况下不可修改,实际上芯来科技的设计内核架构提供了一组mattri[i]_base、mattri[i]_mask('i’指编号),可以让软件来修改PMA,但这里也有规则,有优先级顺序,即只能从低优先级修改成高优先级属性(感兴趣可以自行查找芯来RISC-V ISA spec)

2 PMP

2.1 简介

PMP(Physical Memory Protection)物理内存保护。

RISC-V特权模式及切换 , 有介绍过RISC-V的特权模式,如何限制各特权的访问权限呢,实现安全隔离呢?这里就需要PMP来提供了。

PMP可以提供安全处理和故障隔离功能,对现代处理器来说是非常重要的。PMP 机制适用于所有特权模式为 S 或 U 的指令和数据访问,通过在 M 态下修改每个 hart 对应的控制寄存器,可以指定每个物理内存区域的读、写和执行等访问权限。此外,PMP 机制也可用于 S 态中的页表访问。违反 PMP 机制的访存将被处理器捕获并触发异常

-

核心功能:

- 负责隔离S/U模式下的内存访问,可通过RISC-V可信固件在M-mode下动态配置S/U模式下程序的读、写和执行权限。

- 用于保护安全外设IO,可以通过约束控制设备控制器MMIO地址空间的访问权限来实现。

- 对于安全域共同访问的共享内存,可以通过将该共享内存分配给不同安全域来实现。

- 当HART进行安全域切换时,RISC-V可信固件通过PMP为目标安全域分配可访问的系统资源,这可以通过在M-mode下操作PMP配置表和地址表进行管理。

-

物理内存保护机制:

- 通过配置寄存器pmpcfg和地址寄存器pmpaddr,来定义内存区域访问权限

- 一个配置寄存器和一个地址寄存器组成一个PMP表项(entry),每一个entry对应一段物理地址的范围和权限(R/W/X),一般硬件对表项数量有要求,通常为8或者16,最大64

2.2 配置规则

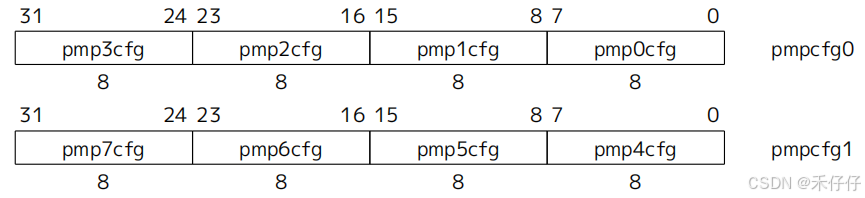

- pmpcfg寄存器

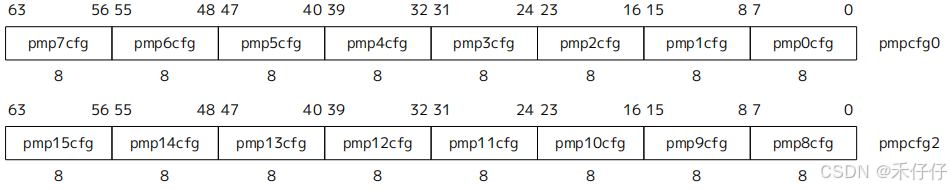

pmpcfg<x>寄存器用于指定 PMP 表项的权限配置寄存器,每个pmpcfg<x>寄存器可以管理四个PMP 表项目

每个表项的权限配置寄存器 pmp<x>cfg 中各控制位域:

| 域 | 位 | 描述 |

|---|---|---|

| R | 0 | 控制数据可读权限: - 1:地址区间可读 - 0:地址区间不可读 |

| W | 1 | 控制数据可写权限: - 1:地址区间可写 - 0:地址区间不可写 |

| X | 2 | 控制代码可执行权限: - 1:地址区间可执行 - 0:地址区间不可执行 |

| A | 4:3 | 控制地址区间模式(详见下表) |

| Reserved | 6:5 | 未使用域(固定为0) |

| L | 7 | 控制PMP表项锁定: - 1:锁定表项 - 0:不锁定表项 |

每个表项的权限配置寄存器 pmp<x>cfg 中的“A”比特域(第 4~3 位)用于控制该表项的地

址区间模式,其编码和模式的含义:

| A | 名称 | 描述 |

|---|---|---|

| 0 | OFF | 空模式,即:没有配置此表项 |

| 1 | TOR | 紧邻下一边界 即区域 X 的结束地址紧邻下一区域的基地址寄存器 pmpaddrX 的值 举例:pmpcfg0设置为TOR,则受保护为[pmpaddr0,pmpaddr1] |

| 2 | NA4 | 4 个字节大小的区域(地址对齐) |

| 3 | NAPOT | 2 的幂次方大小的区域(区域大小起码大于等于 8 个字节,并且地址对齐) |

其中:

-

NA4:Naturally Aligned 4-byte

-

NAPOT:Naturally Aligned Power-of-Two

-

L域中L=1表示PMP entry会被锁定,意味着此时写PMP寄存器和地址寄存器会被忽略。

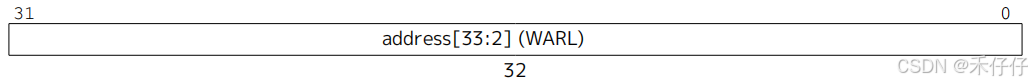

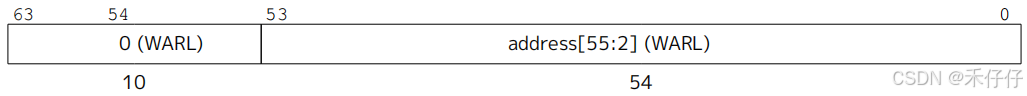

- pmpaddr

保护地址至少四字节对齐,所以在RV32的cfgaddr里写保护地址的[33:2]

保护机制如下:

- 1、pmpcfg.A=2(NA4模式)

定义保护一个4字节对齐的连续地址,若此时pmpaddr0 = 0x20000,则保护0x20000-0x20003。一般用来包含单个寄存器或者单字数据。

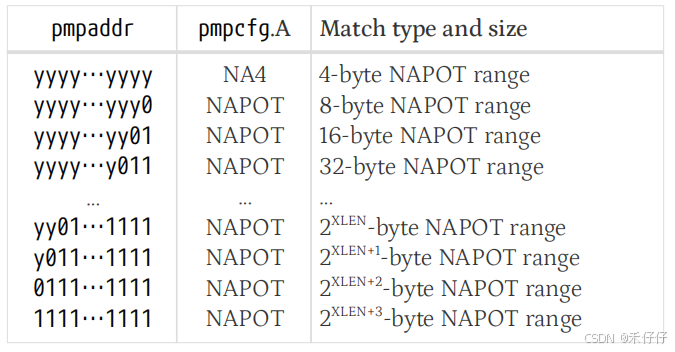

- 2、pmpcfg.A=3(NAPOT模式)

定义保护一个2的幂次方对齐的连续区域,具体由pmpaddr0的低位连续1的个数决定。

如下图所示:

将pmpaddr的值转换成二进制,从低位开始统计连续1的数量(计为n)。则保护区域大小为2^(n+3)字节。

示例:pmpaddr的值为yyyy…y01111,则保护区域大小为:2^(4+3) = 128byte。假如此时pmpaddr0 = 0x2000F,

则保护0x20000-0x2007F。

优先级及原子性说明:

-

1、优先级机制

PMP 条目间采用静态优先级,当区间重叠时,编号小的条目优先级更高。匹配到访问中任何字节的最低编号的 PMP 条目决定本次访问是成功还是失败。 -

2、原子性

匹配的 PMP 条目必须包含访问的所有字节,否则无论 L、R、W 和 X 位的值是什么,访问都将失败。例如,如果一个 PMP 条目被配置为匹配 4 字节区域 0xC–0xF,且为最高优先级条目,那么对区域 0x8–0xF 的 8 字节访问将失败。

RV64说明:

另外上面的配置是针对RV32,对于RV64,每个pmpcfg<x>寄存器,包含8个entry,所以只需要 8 个 CSR 寄存器即可实现与RV32的相同功能。为了与 RV32 保持一致,并降低软件支持成本,RV64 中的 CSR 寄存器编号均为偶数,即 pmpcfg0,pmpcfg2,...,pmpcfg14,奇数编号的寄存器是非法的

pmpaddr,bit[63:54]固定为0,bit[53:0]用于存储地址信息,保护机制同RV32,类比即可,不再举例说明。

NOTE:

- WARL(Write Any Read Legal)

2.3 配置code

OpenSBI(opensbi/lib/sbi/sbi_hart.c)

int sbi_hart_pmp_configure(struct sbi_scratch *scratch)

{int rc;unsigned int pmp_bits, pmp_log2gran;// 获取当前硬件线程(hart)支持的PMP区域数量unsigned int pmp_count = sbi_hart_pmp_count(scratch);unsigned long pmp_addr_max;// 如果硬件不支持PMP,则直接返回0(无需配置)if (!pmp_count)return 0;// 获取PMP的粒度(对齐单位),以2的对数值表示(如4表示16字节对齐)pmp_log2gran = sbi_hart_pmp_log2gran(scratch);// 计算PMP地址寄存器的有效位数(规范定义为实际位数减1)pmp_bits = sbi_hart_pmp_addrbits(scratch) - 1;// 计算PMP支持的最大物理地址:(2^(pmp_bits+1) - 1pmp_addr_max = (1UL << pmp_bits) | ((1UL << pmp_bits) - 1);// 根据是否支持SMEPMP扩展选择不同的配置函数if (sbi_hart_has_extension(scratch, SBI_HART_EXT_SMEPMP))// 使用增强型PMP(SMEPMP)配置rc = sbi_hart_smepmp_configure(scratch, pmp_count,pmp_log2gran, pmp_addr_max);else// 使用传统PMP配置rc = sbi_hart_oldpmp_configure(scratch, pmp_count,pmp_log2gran, pmp_addr_max);/** 特权规范v1.12第3.7.节要求:* 1. 内存访问可能被预取执行,地址翻译可能被缓存* 2. CPU热插拔/非保持性挂起会丢失PMP状态* 3. 需要刷新缓存以保证PMP配置立即生效*/// 检查是否支持监管模式(S-mode)if (misa_extension('S')) {// 刷新当前硬件线程的TLB和地址翻译缓存__asm__ __volatile__("sfence.vma");// 如果支持Hypervisor扩展(H-mode)if (misa_extension('H'))// 额外刷新所有Guest模式的地址翻译缓存__sbi_hfence_gvma_all();}// 返回PMP配置结果(0=成功,非0=错误)return rc;

}

此函数是 RISC-V 安全引导流程(如 OpenSBI)的核心部分,负责:

- 初始化物理内存保护(PMP)机制。

- 根据硬件特性选择传统或增强型配置。

- 确保 PMP 生效后内存访问的安全性。

3 PMA与PMP的协同规则

在RISC-V架构中,PMA(物理内存属性)和PMP(物理内存保护)是两种不同的机制,它们共同作用于物理内存访问的控制。PMA定义了内存区域的固有属性(如是否可缓存、是否可执行等),而PMP则提供了基于特权模式的访问控制(如用户模式是否可以读写某区域)。二者通过静态属性与动态权限叠加进行内存访问保护,下面简单介绍下协同工作的规则

3.1 协同规则

- PMP的权限约束需基于PMA的属性定义

PMP(物理内存保护)的访问控制规则仅在 PMA(物理内存属性)允许的权限范围内有效。例如,若 PMA 将某内存区域标记为 不可执行(Non-Executable),即使 PMP 配置为允许执行(Execute),对该区域的执行访问仍会触发异常。这是因为 PMA 是更底层的硬件保护机制,决定了内存的物理属性(如可执行性、缓存策略),而 PMP 只能在此基础上叠加权限限制。

- 外设寄存器的联合保护机制

对于设备内存(如外设寄存器),PMA 通过设置 不可缓存(Non-Cacheable)属性确保直接访问硬件寄存器,而 PMP 则进一步通过权限配置(如仅允许 M-mode 读写)防止用户程序(U-mode/S-mode)误操作硬件。这种 PMA 属性定义与 PMP 权限控制的协同设计,既能保障硬件访问的可靠性,又能防止越权访问引发的安全风险。

3.2 典型协同流程

上图简单总结了下,PMA与PMP的协同工作时的流程,内存访问时,

- 1、进行地址转换(虚拟地址到物理地址)

- 2、执行PMA检查(验证物理内存固有属性,如可执行性/可写性)

- 3、若失败则立即触发异常;

- 4、通过PMA后进入PMP检查(验证基于特权模式的软件权限,如读/写/执行控制),若失败同样触发异常;

- 5、只有同时通过PMA和PMP双重检查,才允许执行最终的内存访问。

这种分层机制确保了硬件属性与软件权限的协同验证,为系统提供基础安全隔离和可靠性保障。

所以我们在在配置时,需确保PMP规则与PMA属性一致,以避免意外行为。

3.3 ePMP(Enhanced Physical Memory Protection)

ePMP 是 RISC-V 架构中 PMP 的增强版本,通过 Smepmp 扩展实现。它在传统 PMP 基础上增加了关键安全特性,特别针对机器模式(M-mode)提供了更严格的内存保护机制。

关于ePMP后续再做具体补充说明,感兴趣可以阅读RISC-V来学习。

参考:

SiFive U74 手册

The RISC-V Instruction Set Manual (Volume II: Privileged Architecture)

)