痕量分离;长度平行度;stackup:有没有一个脱颖而出?

我已经有一段时间没有看到关于串扰的文章了,所以我决定借此机会为那些可能对为什么精通串扰的 PCB 设计人员和硬件工程师使用各种设计规则来控制串扰感兴趣的 PCB 设计社区中的人简要介绍一下这个主题。在此过程中,我们将确定哪些设计调整为控制远端串扰提供了最大的杠杆作用。

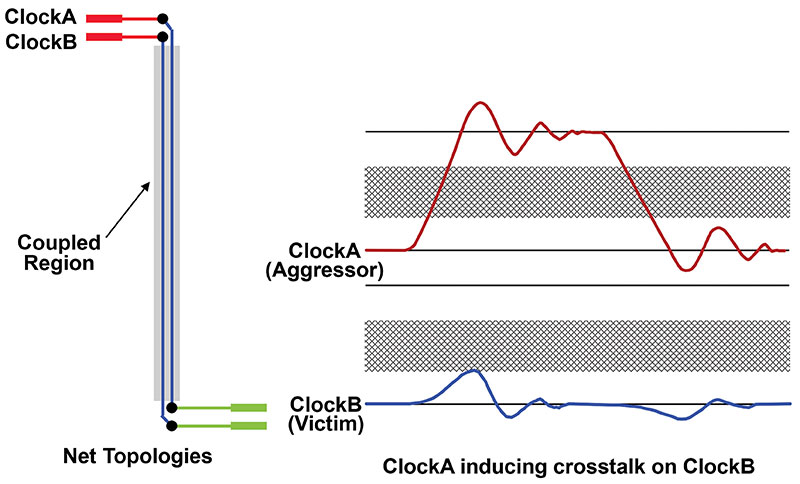

串扰是信号之间产生的不需要的噪声。当 PCB 上的两个或多个网络通过电磁方式相互耦合时,就会发生这种情况(即使它们在导电上根本没有连接)。这种耦合可能发生在两个网络彼此相邻运行任何重要长度的任何时候。当信号在其中一条线路上驱动时,它产生的电场和磁场会导致意外信号也出现在附近的线路上,如图 1 所示。

图 1. 当两个或多个相邻迹线耦合在一起时,就会发生串扰。

许多因素结合在一起会产生不需要的串扰信号:走线耦合的长度、走线之间的距离、它们在 PCB 叠层中的位置、“干扰源”和“受害者”线路上使用的驱动器 IC、线路是否端接等。

除非进行仿真,否则串扰是一种特别难以预测和控制的现象,因为几乎没有办法直观地知道给定耦合会产生多少串扰电压和电流。尽管如此,半保守的设计指南可能是有用的,尽管几乎总是以牺牲电路板空间为代价。

在串扰术语中,“aggressor” 信号或走线会切换并导致串扰。“受害者” 信号或跟踪通过产生意外信号来响应。效果本质上是三维的。受害者可以在同一层相邻,也可以在攻击者的上方或下方(图 2)。

图 2. 受害网可以位于侵略网的上方、下方或附近。

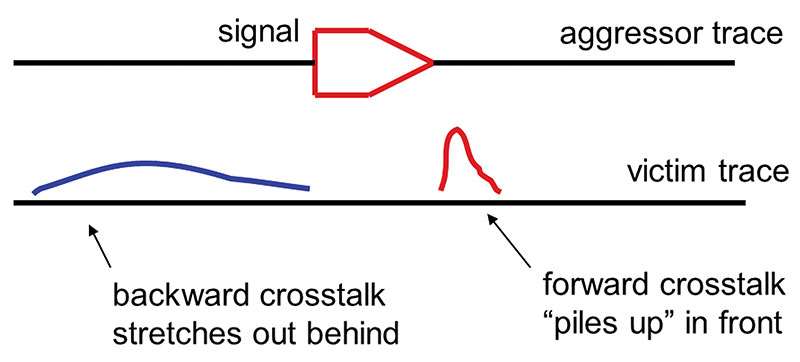

实际上,受害者网络上施加了两个耦合信号:一个正向信号和一个反向信号。“向前”脉冲与干扰源信号一起传播,而“向后”脉冲则从干扰源信号向后传播。受害者远端的串扰称为“远端串扰”或 FEXT,近端的耦合电压称为“近端串扰”(NEXT)。图 3 显示了正向和反向串扰。倒车信号通常在从驾驶员反射后最终向前传播。

图 3. 受害者迹线上的前向和后向串扰图示。

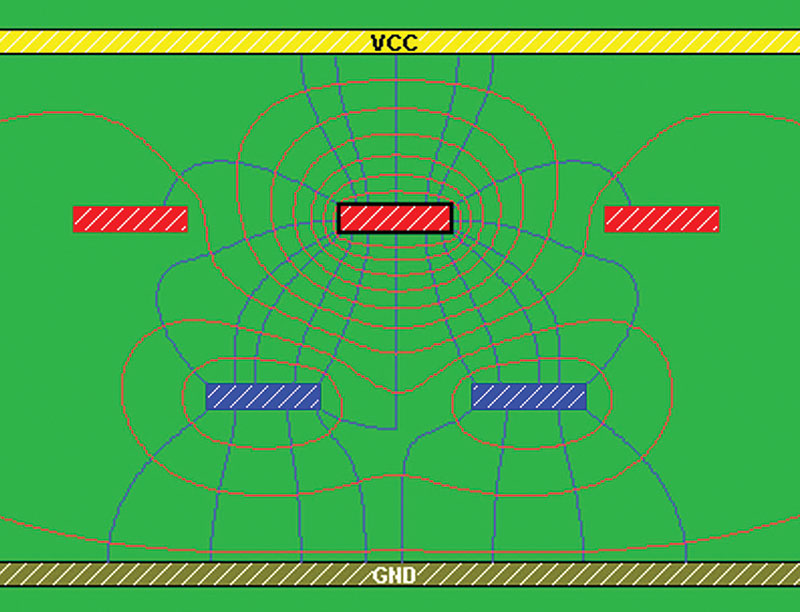

电流通过电场(与图 2 中的走线正交的线路)注入受害者,这是由攻击者和受害者网络之间的电容耦合相互作用引起的。这些相互作用受导体表面积和距离的影响,通常终止于相邻导体。磁场在受害者身上感应出电压。这些是感应(变压器)耦合相互作用,有点圆形——围绕着攻击者和受害者网络。这些相互作用通常不会被导体阻止,因此可以围绕多个相邻导体扩展。

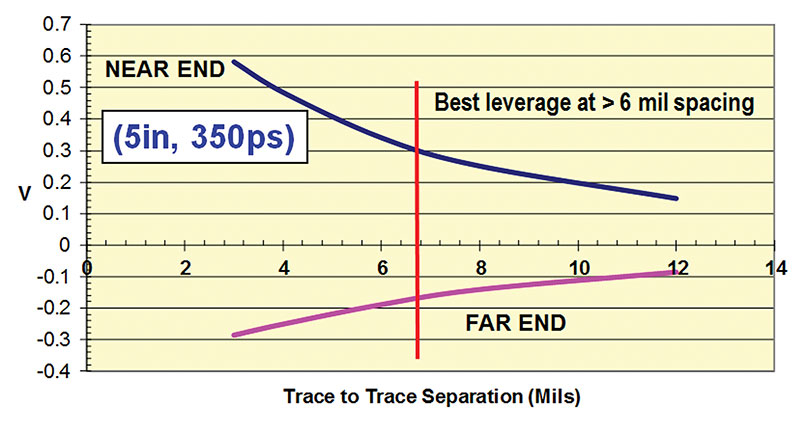

串扰指南。最常见的串扰设计规则涉及迹线到迹线分离。例如,PCB 设计人员可以将 auto-router 设置为 4-mil 走线宽度和 4-mil 间距。当然,这将最大限度地提高 router 的完成度,但最终设计将产生 20 至 60mV 的串扰。将噪声敏感的受害者调整为超过 6 mil 的走线间距可以帮助避免这个问题(图 4)。

图 4. 该图使用两条平行的 5 英寸线,显示 NEXT 和 FEXT 的曲线在攻击者网络和受害者网络之间大约 7 mil 的间距处开始变平。垂直线左侧的间距越窄,串扰越多,垂直线右侧间距越大,好处越小。

由于电场终止于参考平面,因此靠近参考平面的走线减少了串扰。电容性走线到走线耦合与参考平面的距离呈二次方下降,因此与距离最近参考平面 6 mil 或更多 mil 的走线相比,参考平面 4 mil 范围内的走线更不受串扰的影响。对称带状线 - 因为它们不是一个,而是两个参考平面 - 比微带信号具有相对更高的抗扰度。

此外,还需要考虑介电常数效应。高介电常数 (Dk) 使电场集中,导致串扰性能相对较差,在 Dk 和电容串扰之间大致呈线性关系。

示例:总线上的串扰。 假设您正在设计一条总线,并希望保证任何信号上都不会发生超过200mV的串扰。以下是开发适当的 routing constraints 以实现它的过程。现代数字系统中的典型总线包含许多物理并行的走线 – 16、32、64 – 甚至更多信号。但是,要分析此类总线上的串扰,您可以将范围缩小到单个 “victim” 迹线,两端都有 “aggressor” 网络。

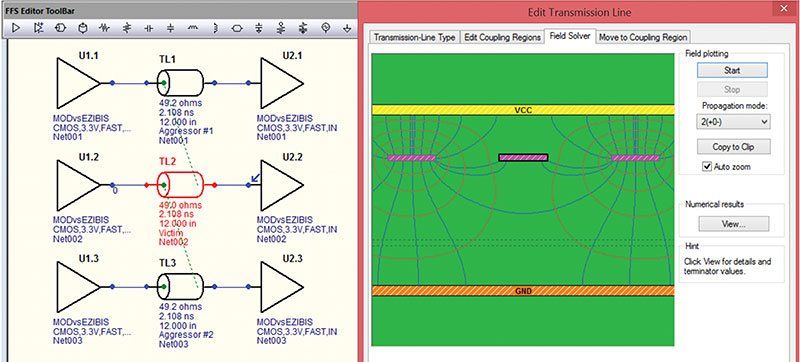

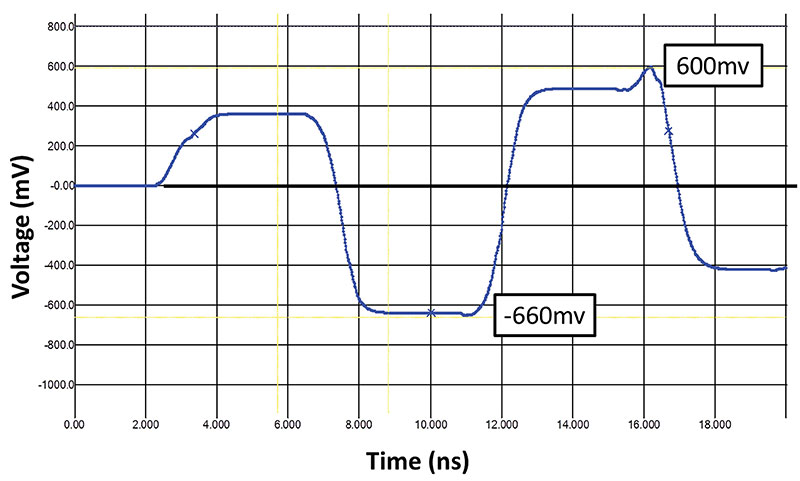

让我们从耦合的共面 6.0 mil 宽 (W) 带状线开始,通过高度为 5.0 mil (H) 的 4.3 Dk 电介质,平行运行12 英寸,走线间距为 8.0 mil (S)(图 5)。使用 HyperLynx LineSim 进行模拟(图 6)显示了远端串扰,以查看初始排列中发生了多少串扰。在两个干扰源网络上的驱动器切换速度为 590ps (0.59ns),并且没有在受扰网络上注入信号,正极约 600mV 的受扰波形将被注入,负极的 660mV 将被注入 – 两者都远远超过了我们 200mV 最大串扰的设计标准。

图 5. 串扰很容易用所示的 aggressor-victim-aggressor 示例来说明。(与 Mentor 的 HyperLynx LineSim 一起显示。

图 6. 受害网络上的远端串扰 (FEXT) 如图 5 所示。

串扰是一种复杂的效应,受许多不同的几何因素影响:例如,驱动器 IC 技术(Tr、Tf、输出阻抗和驱动强度)、走线宽度 (W)、铜重量 (T)、平行线长度 (Lp)、走线分离 (S)、PCB 叠层 [层排序、Dk 和介电厚度 (H)]和线端端接。(串扰通常需要比单线反射更复杂的端接。存在控制串扰的经验法则,但要在控制特定设计成本的同时最大限度地减少串扰,需要一个好的仿真工具。在下一节中,我们将通过一个迭代过程来处理图 5 和图 6 中设计的串扰,看看是否出现了一些合理的设计规则。

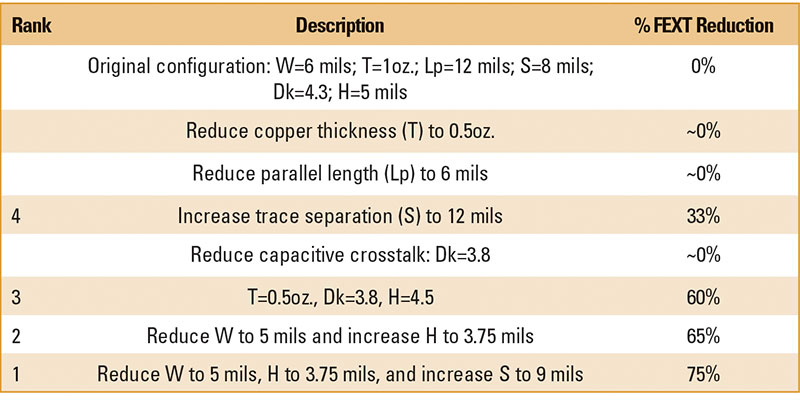

串扰减少技术。有时可能被忽视的串扰杠杆是铜的厚度。在上面的示例中,信号使用了 1 盎司的铜。这对于 signal trace 来说很粗。有人可能会认为减小铜厚度会降低电容耦合,尽管仿真表明结果在实践中并不显著。尽管如此,在本次讨论的其余部分,我们将使用更常见的 0.5 盎司铜。

减少串扰的一种可能技术是减少攻击者和受害者彼此平行的长度。这在布线方面带来了一些实际问题——这些走线在电路板上是平行的,这是有原因的——但看看当并联耦合区域从 12.0“ 减少到 6.0” 时会发生什么是有指导意义的。令人惊讶的是,这根本没有减少串扰;它只是在时域中将峰值串扰幅度向左移动。作为串扰杠杆,仅减少并行性并不像我们想象的那么强大。

减少串扰的另一种常见方法是增加走线之间的分离 S。将走线间隔从 8 mils 增加到 12 mils 将正侧的串扰降低到 400mV,将负侧的串扰降低到 -400mV – 仍然远远超出我们想要的水平,在进行此更改的过程中,我们使用了更多的电路板空间。

除了 trace separation 和 length parallelism 之外,还有很多方法可以影响串扰。有时被忽视的是 PCB 叠层。回想一下,我们从 Dk=4.3 开始。如果我们尝试使用低 Dk 材料(比如 D=3.8)来减少电容串扰,会发生什么情况?通过模拟,事实证明,仅此更改带来的改进可以忽略不计。然而,在使用 0.5 盎司铜并降低电介质的 Dk 的过程中,走线阻抗从大约 50Ω 增加到略低于 57Ω。(请记住:阻抗与走线电容的平方根成反比,走线电容与电介质的 Dk 有关。因此,将目标带状线层和最近的参考平面之间的介电厚度 (H) 从 5.0 mils 减小到 4.5 mils,电容再次增加,将阻抗拉回 50Ω 左右。这些因素的结合使我们更接近目标,导致正侧的 211mV 降至负侧的约 230 mV – 超过 60%,但仍高于我们的 200mV 目标。

减小走线宽度 (W),从而增加阻抗 (Z0),然后缩小介电厚度 (H) 以将阻抗拉回 50Ω 左右,这是减少串扰的另一种可能方法。将 W 降低到 5.0 mils,将 H 降低到 3.75 mils,会产生大约 200mV 的正和负串扰。

通过将走线宽度 (W) 缩小 1.0 mil,总总线宽度(以 mils 为单位)减少了位数减 1。为了获得更多的裕量,同时保持初始设计中的总线总宽度,在间距上再增加一个mil(即,将S从8.0 mils增加到9.0 mils)会产生大量的裕量:正侧为160mV,负侧为170mV。

表 1 总结了对图 5 中拓扑的影响,以及它们对 FEXT 的相对影响,按最坏情况下串扰的相对减少排序。

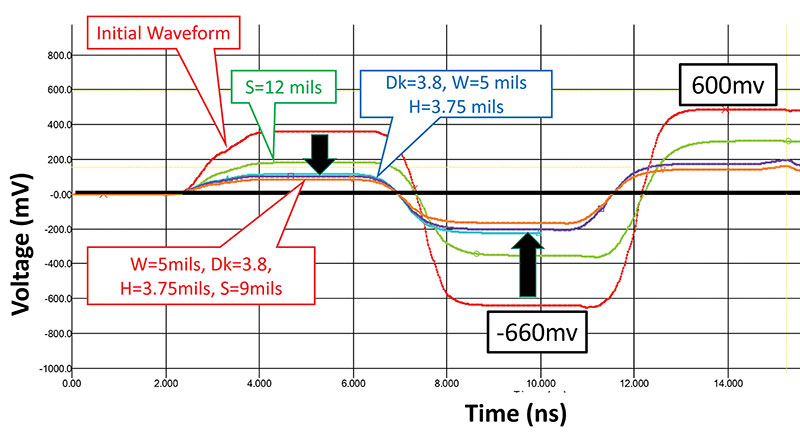

图 7 显示了减少这种特定总线设计中串扰的前四种方法。最终的设计规则是使用 W=5.0 mils、Dk=3.8、H=3.75 mils 和 S=9.0 mils。

图 7. 减少图 5 总线设计中串扰的四种主要方法。得到的设计规则是 W=5.0 mils,Dk=3.8,H=3.75 mils,S=9.0 mils。

离别的思念。 在过去的 10 年里,我一直在与工程师和 PCB 设计师交谈,我听到了很多关于使用更薄的电介质的参考资料,因此对于一些读者来说,本文的内容可能是评论。但我还没有看到一篇文章比较了用于控制串扰的不同杠杆,强调材料选择,特别是层压板厚度在控制远端串扰 (FEXT) 中起着最关键的作用。

在以后的专栏中,我将详细介绍更紧密的电场耦合到最近的参考平面的工作原理,并附带一些视觉效果,也许还会回顾麦克斯韦方程组。

引用

1. Bill Hargin,《印刷电路手册》,第 7 版,McGraw-Hill Education,第 20 章,2016 年。

SQL数据库)

)

![[Java 基础]正则表达式](http://pic.xiahunao.cn/[Java 基础]正则表达式)